来源:内容转载自期刊《微纳电子与智能制造》,谢谢。

摘 要

集成电路是将电子元件依照电路互连“,集成”在晶片上,实现特定功能的电路系统。在当代,集成电路已渗透到社会发展的各个领域,是信息产业高速发展的基础和动力。在经济结构调整中,集成电路产业的战略性、先导性地位凸显,有望从根本上对制造业进行改造,在完成产业升级同时满足国家信息安全的需要。随着需求的不断提升,未来的集成电路需兼具低功耗、小尺寸、高性能等综合素质,传统工艺的改进已不足以满足这些要求。为此,集成电路制造业必须拓展相应制造技术以顺应新的发展趋势。我国集成电路产业近20年来取得了显著发展,总结了国内集成电路产业的发展历程及现状,并对未来发展进行了展望。

1.摩尔定律时代的挑战及技术进步

集成电路发明已届60周年,在学术界和产业界的共同推动下,集成电路产业的发展基本遵循着摩尔定律所预测的节奏,即集成电路上可容纳的元器件的数目 ,约每隔18~24个月便会增加一倍,性能也将提升1倍。摩尔定律的核心即芯片集成度的提高,主要由集成电路制造工艺来实现。因此,集成电路制造在整个集成电路产业链中占据着尤为重要的地位,一方面推动着摩尔定律的演进,另一方面为集成电路设计业实现产品,同时支撑着庞大的集成电路专用装备和材料市场。

在摩尔定律的作用下,单个晶体管的平均价格一直呈指数的趋势逐年下降,如图1所示。在各个技术节点里,都有一些关键的制造工艺技术的进步支撑着摩尔定律的发展。

图1.1968~2002年,单个晶体管的平均价格下降趋势

在摩尔定律时代,芯片制造的工艺技术主要有5个方面的挑战,集成电路从业者通过技术进步不断突破挑战,适应了摩尔定律的发展要求。

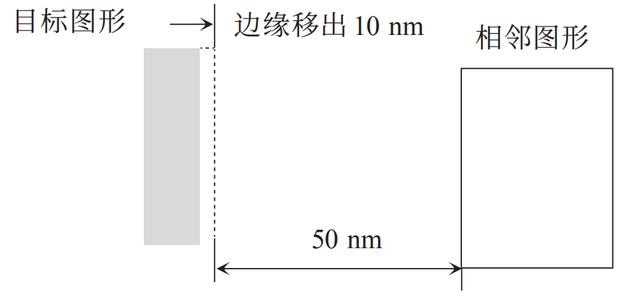

1.1 图形转移跟晶体管CD尺寸密切相关的制造工艺是光刻工艺,在摩尔定律时期,科学家一直在寻求波长更短的光源以达到更高的光刻分辨率。然而在EUV的技术成熟之前,光刻技术所使用的波长长时间停留在193 nm的节点,最新的193 nm浸润式技术在制造80 nm pitch的图形上已经比较困难。为了突破这种挑战,科学家们发明了光学邻近效应修正(OPC)及多重曝光技术。OPC使用较为广泛的一种技术是基于规则的修正,指的是建立一套与图形周边情况有关的规则,使得在这些规则满足的情况下,按照规则定义的要求对图形进行修正,规则的制定依赖于对一组定标图形的精确测定。如图2所示,当100 nm的线条的某一边界距离下一个图形边界的距离大于或等于500 nm时,此边界往外移动10 nm。

图2.光学邻近效应修正的方式示意图

1.2 新材料及工艺自本世纪以来,芯片制造商应用了越来越多的新元素,在器件及工艺优化中使用了64种新的元素。这些新材料的应用支撑了集成电路70%的性能提升,所有新材料的应用都需要大量的工艺和集成实验。如图3所示的石墨烯的应用,在400℃下将石墨烯直接生长在图形化的导线上,其电阻率比沉积铜低2倍,击穿电流密度高1.4倍,电磁化寿命长40倍。另一个新材料的应用是Ge元素的引入,在CMOS FinFET的技术中,应用基于SiGe应力工程的技术,可为高性能低功耗的应用器件提供好的解决方案。

(a)Ta/Cu元素的溅射

(b)400℃下石墨烯在Cu表面的 CVD沉积

(c)SiNx保护层的沉积

图3.应用于后端铜工艺的石墨烯沉积工艺流程示意图

1.3 工艺波动

随着器件CD尺寸的缩小,制造工艺的波动对器件的性能及良率的影响显得越来越大。比如,对于FinFET器件,要求精确的控制调节Vth的掺杂工艺,其波动要求在100个原子以内,而且器件尺寸越小,其对工艺的波动就越敏感。如图4所示,器件Vth的变化主要来源于掺杂(random dopant fluctuation,RDF)、工艺变化(process variation effect,PVE)、功函数波动(work function fluctuation,WKF),而来自界面阱波动(interface trap fluctuation,IFT)的影响很小。

图4.不同类型的波动对器件性能的影响

1.4 新结构从21世纪初,传统的晶体管的沟道尺寸进一步缩小到20 nm及以下的技术节点,但是技术的进一步突破就陷入困难的境地。幸运的是,科学家们创造了数个伟大的CMOS发明,继续推动了器件尺寸的缩小和性能的提高。

(1)为了解决晶体管尺寸缩小带来的短沟道效应,科学家发明了3D FinFet晶体管。鳍式场效应晶体管(fin field effect transistor,FinFET)是一种新的互补式金属氧化物晶体管。如图5所示,Fin是鱼鳍的意思,FinFET命名根据晶体管的形状与鱼鳍的相似性。鱼鳍式晶体管的沟道包括一面水平方向和两面垂直方向 ,这种设计使得栅极能够将介电层的3面都包围起来,栅极的水平方向长已可小于9 nm,显著地降低了栅长。FinFET是基于传统的场效应晶体管的创新设计。在传统的晶体管结构中,其控制栅极属于平面结构,控制电流通过的栅极,只能在栅极的一侧控制电路的接通与断开。而在这种FinFET的构架中,栅门的结构类似鱼鳍的叉状3D架构,可在电路的两侧控制电路的接通与断开。这种设计可以大幅改善电路控制并减少漏电流(leakage),也可以大幅缩短晶体管的栅长。这种鱼鳍式设计使得晶体管的工作电压降低到0.8 V,与传统的场效应晶体管相比,开关速度提高了35%,能耗降低了55%。

(a)传统场效应晶体管

(b)3D FinFET晶体管

图5.传统场效应晶体管与3D FinFET晶体管的结构示意图

(2)为了解决晶体管尺寸缩小带来的漏电流增大的现象,人们发明了High-K metal gate(HKMG)技术。如图6所示 ,HKMG技术是将传统的多晶硅栅极替换成金属材料电极,将介电层材料由SiO2替换成高介电性的材料,比如 HfSiO(N)或HfO2。与传统的CMOS相比,High- K材料能为栅极漏电流带来数量级的下降,金属电极的应用还能提高沟道载流子的迁移率。

(a)传统多晶硅栅极晶体管

(b)HKMG晶体管

图6.传统多晶硅栅极晶体管与HKMG晶体管的示意图

(3)应力硅技术是提高电子和空穴载流子迁移率的一个有效手段,电子的迁移率随着拉应力的增加而增加,空穴的迁移率随着压应力的增加而增加。所以,在PMOS器件上,通常应用锗硅源漏工艺,在沟道产生压应力,能显著提高PMOS沟道空穴的迁移率;而在MNOS器件上,通常使用碳硅源漏工艺,在沟道产生拉应力,能显著提高NMOS沟道电子的迁移率。

1.5 工艺整合及良率提升随着技术的进步,集成电路制造所使用的工艺步骤显著增加。比如说,对于65 nm技术节点,需要大约600步的工艺步骤,而对于14 nm技术节点,至少需要2000步工艺步骤。在半导体生产制造的各个工艺环节,都有可能造成最终产品性能的降低或者失效。良率提升的工作就是找出造成产品失效的环节,提出失效模型,解决工艺难题,提升产品的最终良率。从产品研发到实现量产的整个周期内,整个周期的时间跨度可能达数个季度,在每个阶段都需要对良率进行不断的改善,各阶段的良率表现如图7所示。在产品设计及工艺研发阶段,主要通过器件及工艺流程的建立和优化提升产品良率。在良率提升阶段,通过找出并解决工艺中的系统性失效问题,解决工艺问题引起的随机性缺陷提升良率。在量产阶段,新产品的导入和生产制程的在线管控是重点。在新产品的导入时,需要确定工艺的最优条件,设计对工艺的交叉弱点的检测,以便及时发现工艺异常并作出改善。在生产制程的管控上,要求减少各种异常事件(excursion),如设备故障、操作失误等,快速的问题诊断(trouble shooting),降低关键制程的变异(variation)等。

图7.产品周期各阶段良率增加的表现

以上5个问题也是将来后摩尔时代半导体行业的挑战。如图8所示,在摩尔定律时代芯片的密度、运行速度、功耗、单个晶体管价格的变化趋势,可以发现在摩尔定律时代后期,芯片速度和功耗上的改善速度在逐渐放缓,晶体管的价格基本没有下降甚至会增加。从这点看,摩尔定律会在2015~2025年之间走向终结,如图9所示。

2.后摩尔时代的创新趋势

半导体业界已经意识到,必须通过新的创新推动CMOS技术继续向前发展。当前,业界的各个领先企业及科研机构都在技术革新上作出新的贡献。

2.1 新结构的创新(1)人们认为,TFET结构是低功耗器件的最优结构。使用这个新的结构,器件的Vdd可以降到0.1V。2D异质节TFET器件的栅极长度可以下降到3 nm。实验证明,基于与传统CMOS技术兼容的技术,通过对Si JTFET结构的优化,SSmin可以达到36 mV/dec。而且,基于新的TFET器件的设计,器件的性能及稳定性都能得到提升,电路级别的实验证明,运行速度能提升93%,在工作电压Vdd为0.4V的情况下,功耗能降低66%,器件的稳定性也得到了显著地提升。然而,这种新结构也有3个方面的挑战,比如说JNT结构的制造难度大,工艺的波动较频繁,开关速度较慢。

图8.后摩尔定律时代的集成电路发展特征

图9.摩尔定律失效预测

(2)栅极环包围结构(gate all around,GAA)是另一个控制器件电流的优化结构。GAA结构器件的Ion /Ioff 的比值可达2.8×10⁸。实验证明,使用这种 GAA技术,能将器件的性能推到新的记录。比如说,使用In0.85Ga0.15As纳米线的MOSFET器件,其开启电流Ion在两种条件下可达到555 μA/μm(Ioff=100 nA/μm,Vdd=0.5V),及365 μA/μm(Ioff=10 nA/μm,Vdd=0.5V)。

2.2 新材料的创新(1)在新材料的应用上,SiGe和III-V族半导体的应用是最有前景的技术。在FinFET结构引入到CMOS器件上后,SiGe成为半导体制程里面的一个主要技术领域。在当前的10 nm和7 nm技术平台上,SiGe都在PMOS上有所应用,应用SiGe FIN技术能显著提高器件性能,特别是对于沟道空穴的迁移率的提高。然而SiGe的应用也面临很多难题,比如说defect的控制、纳米尺度的电荷输运机制等都是需要研究的课题。

(2)碳纳米管材料由于其具有高频率低功耗的特点,在未来计算芯片上也有广泛的应用前景。对于5nm节点的器件,碳纳米管晶体管(CNTFET)相对于FinFET晶体管更有优势。然而,对于CNTFET的应用也有很大的挑战,主要是生长制造上存在严重的波动性。

(3)二维(2D)材料也有非常好的应用前景,当前对二维材料研究还处在材料性质的研究上,比如说二维晶体材料(MoS2,WSe2,BN,石墨烯)的性质。研究发现,MoOx作为contact材料具有较高的功函数,可以用于PMOS的介电层。

2.3 新的工艺设计在后端的金属互联工艺里,业界开始应用一些新的结构设计,比如说空气隔离技术,可以用来弥补低K材料的不足。空气隔离可以使用PECVD工艺在非常高的沉积速率的条件下产生。实验证明,空气隔离技术可以将RC降低。当前,半导体业界对3D芯片的重视越来越多,主要是因为这种芯片能够将逻辑处理器和存贮器集成在一起,而空气隔离技术能够降低这种芯片的信号传输延迟效应,提高芯片性能,所以空气隔离技术在未来具有非常广阔的应用前景。

3.我国集成电路产业的发展历程

集成电路制造是半导体产业的核心基础,是高度技术密集型产业,在集成电路产业链中处于基石的位置。中国在全球半导体市场中的份额从2000年的7%持续快速增长,到2015年占比达到45%。当前,我国大陆集成电路制造产业正处于高速发展期,在销售规模、技术升级、产能扩展和规划新生产线建设方面都取得显著进展,是全球集成电路产业增长最快的地区,也是全球半导体贸易最活跃的区域。但是,当前我国大陆集成电路制造业规模占全球不到10%,集成电路产业链的装备、材料及关键零部件在全球的占比均不到1%,制造技术水平与国际先进工艺技术还有3代差距的事实与我国作为集成电路消费大国的地位严重不匹配。

2017年我国集成电路制造业的销售规模为1448.1亿元,同比增长28.5%,占我国电路产业链的比重为26%。整个“十二五”期间我国集成电路制造业的年复合平均增长率达到15.3%的高水平,2011~2017年年均复合增长率为22.35%,特别是近3年均以超过25%的速度高速增长,增速在集成电路产业链中保持第一,为我国建设自主可控的集成电路产业体系打下了坚实基础。从集成电路制造的业态来看,当前我国集成电路制造企业以纯晶圆代工企业为主。从技术发展水平来看,当前国内集成电路制造产业正处于加快45/40 nm技术产能扩充,32/28 nm技术量产并逐渐形成规模生产力,16/14 nm完成研发并进入客户产品导入阶段,预计2019年形成量产能力。国内领先的制造企业也已经积极投入10 nm以下技术研发。得益于我国集成电路市场规模的快速增长,越来越多的国内集成电路制造企业跻身全球前列。十二五以来,在我国各地纷纷建设集成电路制造工厂 ,集成电路制造业呈现出一派繁荣的景象。

但是,与表面繁荣相对的是我国集成电路产业与世界全面的差距,特别是2018年中兴事件的发生,让全国上下对我国集成电路产业的现状有了清晰的认识。

就我国的集成电路制造技术而言,研发投入严重不足,高端人才及其匮乏。制造技术落后国际最先进水平约3个技术代。落后的技术造成的直接后果就是制造企业无法获取最新技术诞生初期的高额利润,造成之前投入的研发成本和后续进行量产资本支出的回报周期大大增长,一般会超过10年,直接限制了制造企业规模的扩大。目前国内集成电路制造企业一方面出于自主性需求必须加紧追赶国际先进技术,另一方面新一代技术形成量产能力后迫于国际领先企业降价压力只得低价抢单维系自身生产。一方面是研发的持续高投入,另一方面是量产的长期低回报,陷入两难境地。

实际上,国内集成电路制造企业的规模和盈利能力根本无法对标国际领先企业巨量且持续不断增长的研发投入。即使通过国家科技重大专项等研发项目对企业研发进行支持,但还是与国际巨头每年动辄20多亿美元的投入差距巨大。国内集成电路制造企业只能把有限的资源用于技术的追赶,无法进行先导技术的研发投入,更不可能对未来的技术进行投入。这样直接造成国内的集成电路制造高端人才很难由自身产生,只能从国际先进企业招募,并且加入到国内企业的高端人才 ,由于缺乏前沿技术研发的机会,将失去对领先技术的了解,丧失持续研发的能力。

国内集成电路制造企业本身的营收规模和盈利水平除了无法在先进技术研发上持续高投入,在成熟工艺节点的工艺拓展以及产能建设上也心有余而力不足。

相对于集成电路先进制造企业而言,与其配套的国内集成电路专用装备、材料和零部件产业的起步时间更晚,是2008年伴随国家科技重大专项的启动而正式发展起来的,经过了10年的发展,就成熟工艺而言,实现了多点上零的突破,个别产品也进入到先进工艺的研发和量产应用中。

对于集成电路专用设备,集成电路从生产工艺领域讲有10大类工艺设备,加上工艺监测设备共分11大类,目前各个大类都有国产设备处于研发验证到量产的不同阶段。具体到关键工艺设备,如铜互连物理气相沉积设备(北方华创科技集团股份有限公司),中束流离子注入设备(北京中科信电子装备有限公司),快速热退火设备(北京屹唐半导体科技有限公司),浅沟槽隔离与通孔介质层、钝化层等离子体刻蚀机(北方华创科技集团股份有限公司、中微半导体设备(上海)股份有限公司),二氧化硅薄膜等离子体增强化学气相沉积设备(沈阳拓荆科技有限公司),氧化层化学机械研磨设备(天津华海清科机电科技有限公司),单片清洗机(盛美半导体设备(上海)有限公司 ,北方华创科技集团股份有限公司)及部分附属装备如北京京仪自动化装备技术有限公司的恒温冷却设备 ,尾气处理设备及中国科学院沈阳科学仪器股份有限公司的真空干泵可以做到部分替换进口。虽然最尖端的光刻设备还处于技术攻坚阶段,但是相信在不久的将来光刻设备也会实现国产化。

对于集成电路材料,制造领域用生产材料分为8大类别,国产材料已经在研磨液、电子特气等上取得不错的成绩,主要项目已经都有国产材料替代产品:研磨液、特气、靶材、硅片、化学品等,核心部分如靶材(宁波江丰电子材料股份有限公司/有研半导体材料有限公司)、研磨液(安集微电子(上海)有限公司)、光阻(北京科华微电子材料有限公司)、化学品(浙江凯圣氟化学有限公司HNO3、上海新阳半导体材料股份有限公司CuSO4)、气体(中国船舶重工集团公司第七一八研究所NF3/WF6、广东华特气体股份有限公司CO2、江苏南大光电材料股份有限公司PH3/BF3)等均有部分替代进口 ,目前重点致力于开发其他材料高单价、高使用量等材料,如光阻、硅片和化学品如硫酸、铝线清洗液、双氧水等及突破国外技术封锁、垄断的产品,如研磨垫、光阻、特殊化学品等。

整体上的发展态势非常好,但是面临与制造企业相似的困境。一是技术研发需要大投入,另一个是企业规模小,单靠企业自身能力无法兼顾研发与自身规模发展的需求。

问题很多,特别是从产业链的每个点自身的角度上看发展都遇到困境,但是如果把整个集成电路产业链的整体串起来看,最关键的问题还是产业链上各点的协同发展问题。以中国的制造业为例,现在中国制造(Made in China)是中国的一张名片,虽然在一些高科技领域和基础领域有欠缺,不过在很多领域中国制造都是强大的,其中一个非常关键的原因是都有健全的产业链配套。再具体一些可以参考近年来随着产业链配套的逐步完善,中国在光伏产业和LED产业上都逐步成长到国际领先地位。

要解决集成电路产业链协同发展问题正好可以发挥我国体制上的优势。从成熟工艺入手,支持55 nm、40 nm、28 nm等成熟工艺技术平台的拓展性研发,从政策上鼓励和加强国内终端设备企业、集成电路设计企业、制造企业与装备/材料/零部件企业的合作,使用国内装备、材料和零部件企业的产品,将企业的制造技术供给与日新月异的产品制造需求更好的结合起来,这样就有可能将国内整个集成电路产业规模做大。国家持续加大对于先进工艺研发的投入加速缩短技术上与国际的差距,同时,重点布局后摩尔时代新技术,新结构、新材料、新原理器件及其制造技术。依托目前国内领先的集成电路制造企业,以规模量产为终极目标,探索后摩尔时代新技术,鼓励产业界与学术界人才交流,建立双向流通的长效机制,为国内自主知识产权的科研成果向产业转化探索新路径。这样在集成电路产业做大的同时也会让集成电路产业技术做强。

文献来源:

康劲, 吴汉明, 汪涵. 后摩尔时代集成电路制造发展趋势以及我国集成电路产业现状[J]. 微纳电子与智能制造, 2019, 1 (1): 57-64.

KANG J, WU H M, WANG H. Development trend of integrated circuit manufacturing in the Post-Moore Era and the current situation of China's integrated circuit industry[J]. Micro/nano Electronics and Intelligent Manufacturing, 2019, 1 (1): 57-64.

《微纳电子与智能制造》刊号:CN10-1594/TN

主管单位:北京电子控股有限责任公司

主办单位:北京市电子科技科技情报研究所 北京方略信息科技有限公司

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2212期内容,欢迎关注。