很多朋友在学习FPGA的时候会发现模块划分很令人头大,今天我就通过明德扬温度检测工程来与大家分享一下本人的划分思路。

明德扬温度检测工程是基于FPGA的一个实用项目,可以在明德扬的MP801开发板上进行实验学习。本工程功能虽小,但基本上涉及了FPGA的常见功能,如接口传输、指令解析、外设的控制等,是比较好的入门工程。

一、模块划分要点总结

1、列出项目的功能要求(客户提出的产品功能要求)

2、画出硬件的系统结构框图(添加外设)

3、框图中每个外围接口都对应有一个接口转换模块

接口转换模块的作用是将外围器件的接口时序转为通用的接口时序,或者将通用接口时序转换为外围器件接口时序,这样使得FPGA内部其他模块不用再关心外围接口的时序了。

MDY规范通用接口时序:

- data以及对应的vld,传输单个数据格式

- MDY的包文格式,din,vld,SOP,EOP,MTY,ERR

- wren,waddr,wdata;rden,raddr,rdata,rdata_vld

4、考虑是否涉及指令系统(操作码 数据格式)

上位机,例如PC,ARM,DSP或者其他的器件,只涉及到一个接口,但是却有很多指令或者命令功能要发送,因此就需要一个指令系统。

指令系统一定会涉及到命令、地址和数据。这种情况,肯定会有一个“寄存器解析模块”,根据命令、地址和数据,改变相应的寄存器的值。

5、考虑外围器件是否涉及寄存器配置

项目中有某些外设,上电工作前需要进行配置才能按要求工作。因此需要对外设内部寄存器进行读写,这一流程是通过FPGA来进行配置。

遇到这个情况,使用MDY推荐的模块寄存器配置结构:

寄存器配置表模块 寄存器读写配置模块 外设配置接口时序转换模块

6、根据实际情况,增加、补充或者拆分,优化对应模块,随时调整

原则:根据接口信号,看模块间是否方便对接。接口就决定了模块功能。所以在这一层的调整,一定要清楚接口的定义。

7、考虑是否涉及多路进一路出,要用FIFO

调度FIFO要考虑自身带宽能否满足多路一起突发发送时的数据量情况。如果带宽不满足,就要要输出给上游模块RDY信号。此时RDY信号有效取决于自己设置FIFO的Almost Full信号。如果带宽满足则不必设RDY信号。

8、考虑是否涉及到速率匹配问题,要加上RDY信号或者FIFO

首先考虑与外围器件通信的接口上是否需要rdy信号(FPGA内部运行频率往往与设接口速率不一致),然后考虑FPGA内部模块间数据带宽是否不一致,有等一等的情况。

二、温度检测案例分析

接下来根据上面的总结的要点,通过实际项目案例来分析一下FPGA内部功能模块是怎样划分的。这里我们选取已经做过的温度检测项目,接下来按照上面总结的模块划分步骤,一步步完成模块初步划分!

1.列出项目的功能要求

本项目功能要求:上位机通过发送一系列不同命令给FPGA,FPGA接收到指令后执行各个指令对应的操作。同时将DS18B20采集到的温度值实时在数码管上实时显示出来并传给上位机。要求上位机可以发送命令设置报警温度上限和下限值。当温度值超过温度上限或者下限,蜂鸣器就开始鸣响。可以发送命令关闭或打开数码管显示。

功能分析:

- 上位机发送命令给FPGA(开关数码管显示、开关蜂鸣器、复位温度传感器、开启温度转换,读转换后温度值、设置报警温度上限下限值);

- 读写DS18B20;

- 数码管显示;

- 数码管显示开关控制;

- 计算温度值;

- 将计算后的温度值发送给上位机;

- 设置温度上限、下限;

- 蜂鸣器开关控制。

2.画出硬件系统结构框图

根据步骤1总结出的功能要求,找到除FPGA外需要哪些外围器件。

外围器件总共需要四个:

- PC

- 数码管

- 温度传感器DS18B20

- 蜂鸣器

画出系统框图如下所示:

3.框图中每个外围接口都对应有一个接口转换模块

首先要思考PC与FPGA通信需要哪种方式?

上位机PC与FPGA通信既有发送也有接收,由于PC发送命令给FPGA的速度慢于FPGA回传温度值给PC的速度,所以上位机PC与FPGA通信接口速度取决于FPGA回传温度值给PC的速度。

查阅手册如上图所示,得知DS18B20转换一次采集的温度值需要750ms。所以FPGA与上位机通信接口速率大于750ms就不会丢传数据。因此选用串口作为上位机与FPGA的通信接口足够满足要求了。

- 数码管段选位选接口模块:完成数码管位选和段选的输出

- DS18B20单bit转换接口模块:DS18B20是单总线协议,只支持1bit数据传输,所以需要将MDY规范接口转换为1bit

- 蜂鸣器开关使能接口模块:完成蜂鸣器开关使能

将串口接口转换模块功能细分为“串口接收串转并模块”和“串口发送并转串模块”,进一步转化为符合MDY规范的接口。如下图所示:

本项目涉及指令系统,上位机需要发送指令给FPGA,进而配置温度传感器,配置温度报警上限和下限值,同时可以发送指令控制数码管显示关闭,蜂鸣器开关。因此,系统框图中需要加入“寄存器解析模块”,如下图所示:

本项目中,DS18B20需要配置内部寄存器,但是本项目并没有采用MDY模板的方式(读取配置寄存器表的方式来对DS18B20进行配置),而是通过上位机发送配置命令,解析配置寄存器值再对DS18B20进行配置。

6.根据实际情况,增加、补充或者拆分独立对应模块,随时调整

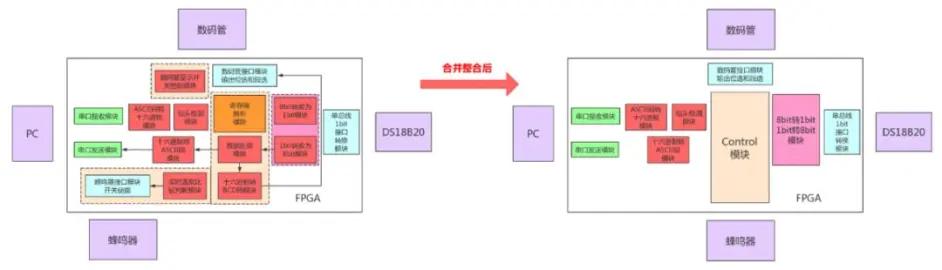

到第6步,根据数据流向,需要对模块间的接口进行详细分析了,补充模块或者将功能相同的模块合并。

首先,从串口接口方向思考,

- 接收到的数据是上位机发来的ASCII码,为了方便FPGA对指令解析,需要将ASCII码译码,转化为对应的十六进制。因此需要一个ASCII码转8bit十六进制模块;

- 接下来,需要对接收包文的包头进行检测,符合正确包头条件的包文保留,否则丢包处理。所以需要一个包头检测模块,用来过滤接收到的有效包文;

- 经过寄存器解析模块后,会将指令解析出来,根据指令功能要求可能分别发送给DS18B20、数码管显示开关控制模块、数码管段选位选接口模块、蜂鸣器控制接口模块;

- 寄存器解析模块发送过来的是8bit数据,不能直接发送给DS18B20(18B20只接收单bit),所以在寄存器解析模块和单总线转换接口模块之间需要一个8bit转换为1bit模块;

- 温度报警功能需要做判断实时温度是否大于上限值,是否小于下限值。所以需要一个实时温度值比较判断模块;

- 然后,从DS18B20方向思考;

- 采集到的温度数据,通过单bit接口转换模块传给FPGA的是单bit数据,为了后面方便FPGA对数据进行处理,需要将1bit转换为8bit。所以需要一个1bit转8bit模块;

- 8bit温度数据需要经过计算处理,因此需要一个数据处理模块;

- 上位机只显示ASCII码格式数据,为实现温度值在上位机上能显示,需要将8bit温度值转换为ASCII码,所以需要一个8bit十六进制数据转换为ASCII码模块;

- 经过数据处理后的结果是十六进制,而数码管显示的是BCD码,为了实现数码管上显示正确数据,因此需要一个十六进制转BCD码模块。

完善后如下图所示:

接下来将功能互斥、数据流向相关,接口一致的模块做合并化简处理,如下图所示:

本项目数据流方面没有涉及多路进一路出的问题,不需要考虑此处的FIFO问题。

8.考虑是否涉及到速率匹配问题,要加上RDY信号或者FIFO

本项目涉及速率匹配问题。

首先考虑与外围器件通信的接口上是否需要rdy信号。

与DS18B20通信是通过寄存器解析模块解析出对DS18B20的操作指令,发送给8bit转1bit模块,因此需要考虑DS18B20能否时刻响应操作指令?

这个问题在选择上位机与FPGA的通信接口时,已经考虑过了,串口的速率小于FPGA写DS18B20速率的。

查阅手册得知,写一次1bit的数据给18B20需要63us,8bit需要63*8=504us,小于串口发送一次8bit指令给FPGA时间1000000us/9600*8=833us。

所以串口接收数据通路上不需要考虑缓存FIFO问题。

在单总线1bit接口转换模块中,由于写DS18B20时序速率远小于FPGA内部读写频率,需要告知8bit转1bit模块每写1bit数据要等一等,待时序满足发送完1bit时序要求后,再发送新的1bit数据。所以在单bit接口转换模块与8bit转1bit模块间需要设rdy信号。

接下来考虑一下串口发送端。由于串口发送模块进行并串转换需要时间,因此串口发送模块需要告知上游十六制转ASCII码模块等一等,因此在串口发送模块与十六进制转ASCII码模块间需要设rdy信号。

由于串口发送模块并串转换需要等待,从而导致十六进制转ASCII码模块也需要缓存control模块发来的数据。因此十六进制转ASCII码模块中需要引入FIFO。

最终得到的模块图如下所示:

到此,根据模块划分步骤一步步做下来,温度检测工程的模块划分雏形初步已经完成。具体实践中需要根据FPGA内部信号的调整,随时拆分或独立来增减功能模块。

以上就是我做模块划分的基本思路,大家有什么问题可以评论区留言

,