11年能发生什么?

网络平台从天涯论坛、百度贴吧变成微博、抖音;手机霸主从HTC、诺基亚变成苹果、三星;大学新生三件套从床上三件套变成“苹果三件套”。而这一系列变化的背后离不开芯片的发展。2011年,人们还在为芯片晶体管规模创新纪录达39亿个而欢呼,11年后,人们已经被高达1140亿个晶体管的芯片所震撼。

即使听上去如同天方夜谭,但11年,已经足够让这个高科技产业发生翻天覆地的变化。纵观芯片发展历史,“极限”两字可以说是存在于每个时代,但无一例外都被一一突破。从22nm工艺节点推出3D晶体管之后,芯片产业仿佛打通了任督二脉,Flash、封装、甚至NAND,都开始走向3D,芯片3D时代悄然已至。

迈出第一步的3D晶体管

晶体管是最早实现3D化的,毕竟按照摩尔定律,晶体管的数量与芯片性能息息相关,在平面晶体管时代,22nm基本就是大家公认的极限了,为了突破这个工艺极限,FinFET晶体管诞生了。

FinFET确切的说,是一个技术的代称。世界上第一个3D三维晶体管是由英特尔在2011年5月宣布研制成功,当时英特尔称其为 “Tri-Gate”( 三栅极晶体管)。早在2002年,英特尔就已经提出了相关技术专利,花了将近10年完善,并在2011年年底用Tri-Gate技术量产22nm工艺的新一代处理器lvy Bridge,于2012年初正式发布。虽然叫法不同,但Tri-Gate的本质就是FinFET。

图源:英特尔

-

FinFET 晶体管

FinFET晶体管又叫鳍式场效应晶体管,由3D晶体管之父胡正明教授于1999年发明。相较于平面晶体管,FinFET运用立体的结构,对栅极形状进行改制,闸门被设计成类似鱼鳍的叉状3D架构,位于电路的两侧控制电流的接通与断开,大幅度提升了源极和栅极的接触面积,减少栅极宽度的同时降低漏电率,让晶体管空间利用率大大增加,让电路更加稳定,同时也达成了半导体制程持续微缩的目标。

而胡正明教授在发明了FinFET晶体管之后,又投身产业界,2001~2004年期间担任台积电CTO。在其任职期间,台积电于2002年制造出操作电压仅0.7伏特的25纳米晶体管,命名为“Omega FinFET”。

上述提到,英特尔是最先推出商业化FinFET的企业,但由于其14nm推迟了整整两个季度,因此被台积电、三星、格芯等代工厂迎头赶上。

三星方面,2013年1月,新思科技宣布采用三星的14LPE工艺成功实现了首款测试芯片的流片。2014年,三星还和格芯联合宣布达成新的战略合作,将共同为客户提供14nm FinFET制造工艺。

台积电则是在2012年10月16日的年度大会中,宣布制订了20nm平面、16nmFinFET和2.5D发展蓝图,并表示将于2013年11月开始生产16纳米FinFETs。在台积电宣布前一个月,格芯已经宣布在2014年开始提供23纳米FinFET。

不过随着芯片制程的不断缩小,FinFET晶体管也遇到了发展瓶颈。台积电首席科学家黄汉森曾表示,在16nm的制程中采用FinFET架构,每个晶体管可以有很多的鳍,但当制程逐渐缩小的时候,鳍的数量也会随之减少。因为不可能有0.5个鳍,所以当制程越往下走、空间越来越小的时候,FinFET最特别的垂直设计将会碰上空间跟技术上的挑战。

之前人们都认为5nm将是FinFET的极限,但2020年台积电打破了这个瓶颈,其在2020年第一季的法人说明会上,透露了3nm将继续采取FinFET晶体管技术。而台积电3nm也预计将于今年下半年出货。不过,这个立体结构的微缩也非无极限,3nm似乎真的已经是极限了,从当前的消息来看,台积电到了2nm也将转采其他的技术,也就是下面要说到的GAA

-

GAA FET 晶体管

GAA全称Gate-All-Around,是一种环绕式栅极晶体管技术,被认为是FinFET技术的升级版。与FinFET的不同之处在于,GAA通过使用纳米片设备制造出了MBC FET(多桥通道场效应管),其设计通道的四个面周围有栅极,减少漏电压并改善了对通道的控制,这是缩小工艺节点时的基本步骤。

由于GAAFET 晶体管只在先进制程中有所采用,所以能参与其中的只有三星、台积电、和英特尔三家巨头。

三星自称在2002 年就对GAA 保持关注并投入研究,并于2019年宣布,将在3nm制程世代,改采GAA技术,作为FinFET之后的接班制程。根据三星的说法,与7nm制造工艺相比,3nm GAA技术的逻辑面积效率提高了45%以上,功耗降低了50%,性能提高了约35%。据悉,搭载此项技术的首批3nm三星芯片将于今年上半年实现量产。

英特尔方面,2020年年初《Profesionalreview》曾报导,英特尔在5纳米节点上将会放弃FinFET电晶体,转向GAA环绕栅极电晶体。不过从英特尔去年公布的未来五年的芯片制程工艺的技术路线图来看,预计要在2024年的Intel 20A(相当于我们说的2nm)制程上才会用到RibbonFET即英特尔的GAA技术。

图源:英特尔

对于台积电2nm制程将采用GAA晶体管好像已成产业内默认的事实,不过笔者搜寻资料发现,台积电官方关于2nm并未给出明确的说法,最初是在2020年7月,据台湾经济日报报道,台积电2nm技术研发有重大突破,已成功找到路径,将切入GAA技术。而在日前2022年第一季度财报电话会议上,虽然台积电总裁魏哲家透露2nm计划2024年预生产,2025年投产,但当分析师询问“有关在 N2 上台积电首次使用 GAA FET,逐渐取代 finFET”的问题,魏哲家也是避而不答。

不过台积电(南京)有限公司总经理罗镇球曾在去年年底透露,台积电研发 Nanosheet / Nanowire 的晶体管结构(类似 GAA)超过 15 年,已经达到非常扎实的性能。

台积电2nm是否真的采用GAA,或许只能交给时间来揭开这个谜底。

冲向200层的3D Flash

从时间上看,第一个3D晶体管和第一代3D NAND闪存芯片推出的时间相差无几。2011年,英特尔推出世界上第一个3D三维晶体管,2012年三星推出第一代3D NAND闪存芯片,也是第一款32层 SLC V-NAND SSD——850 PRO。

闪存走向3D也是发展的必然趋势,毕竟这些年,我们的网络社交方式从文字到图片再到视频,数据量呈指数级增长,平面 NAND已达到其产能发展的极限,再发展下去只会影响其性能、耐用性和可靠性。为了能在有限的空间里存储更多的数据,也为了追求更高的存储密度,闪存工业也开始向3D迈进。

最开始是东芝在2008年开发了3D NAND结构BICS,4年后,三星在2012年推出了第一代3D NAND闪存芯片,随后,东芝、西部数据、美光等存储大厂接连跟上,拉开了3D NAND 层数之战的序幕。

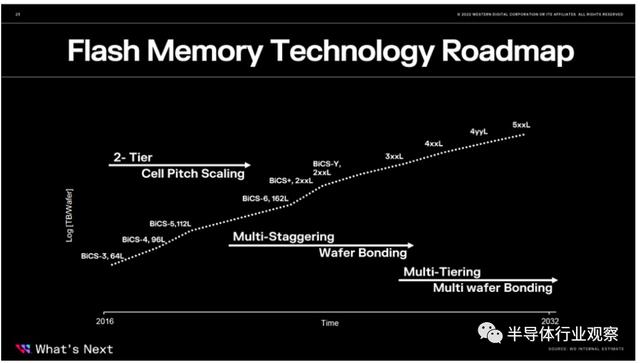

2014-2023年的世界领先存储公司的闪存路线图

图源:TechInsights

对于3D NAND,层数越高,可具有的容量就越大,时至今日,3D NAND的层数厮杀已经迈入200层。今年2月,有韩媒报道称,三星电子将在今年底最晚明年上半年推出超过200层的第八代V NAND产品,采用双堆栈技术,预计率先推出224层NAND产品,与上一代176层NAND产品相比,第八代V NAND可以将生产力和数据传输速度提高了30%。有业内人士表示,三星是目前业内仅采用单堆栈技术实现128层NAND Flash的厂商,采用双堆栈技术的200 层NAND产品也被认为是超高技术领域,技术挑战也十分严峻。

西部数据闪存业务部门负责人、执行副总裁Robert Soderbery在5月投资者活动日中公布了其SSD产品路线图,并预言3D NAND即将进入200 层堆叠,西部数据称其为BiCS 。据介绍,西部数据下一步要推出162层的BiCS6闪存,预计2022年底开始量产采用QLC和TLC配置的BiCS6 3D NAND,而176层的NAND也在制造中。此外,西部数据技术路线图显示将在2032年达到500 层堆叠。

图源:西部数据

美光近日也发布了业界首个 232 层堆栈的 3D NAND Flash芯片,虽然暂时还没有公布232层3D NAND闪存芯片的具体参数,但可以知道采用的是CuA架构,初始容量为1Tb(128GB),并预计在 2022 年底左右开始量产。美光透露,其正在批量生产176层闪存芯片,而作为第五代3D NAND的此款芯片将在2022年之内完成自己的历史使命。此外,美光还就500层以上闪存制定发展路线图,只是尚未披露具体时间表。

图源:美光

相比之下,SK海力士近期在NAND层数上的新闻并不多,不过早在2020年,SK海力士就已经宣布完成了业内首款多堆栈176层4D闪存的研发。

我国方面,长江存储于2018年研发了32层3D NAND芯片并在年底量产,2019年量产了基于Xtacking架构的64层256 Gb TLC 3D NAND闪存。2020年,长江存储宣布,其128层QLC 3D闪存(X2-6070)研制成功。而在近期,有业内人士透露,长江存储最近已向一些客户交付了其自主研发的192层3D NAND闪存的样品,预计将在今年年底前正式推出产品。

对于3D NAND未来发展,SK 海力士曾预计 3D NAND 可以扩展到多达 600 层,从这方面来看,相关制造工艺的线性推进策略还能将持续数年。

火爆的3D封装

3D封装在前段时间也是狠狠火了一把,引爆点在于苹果在3月9日凌晨推出的M1 Ultral芯片,就是笔者在开头提到的那个拥有1140亿个晶体管的芯片,而该芯片采用的就是台积电的3D Wafer-on-Wafer封装技术。

随着芯片越来越复杂,芯片面积、良率和复杂工艺的矛盾难以调和,3D封装是发展的必然趋势。与传统的封装相比,3D封装技术有望提供更高的芯片连接性和更低的功耗。一般来说,3D封装就是将一颗原来需要一次性流片的大芯片,改为若干颗小面积的芯片,采用引线键合、倒装芯片或二者混合的组装工艺,也可采用硅通孔技术进行互连,组装成一颗大芯片,从而实现大芯片的功能和性能,而这种小面积的芯片就是Chiplet。

从当前局势来看,各大IDM厂、晶圆代工厂、封测厂等头部企业都已积极布局3D封装。

在晶圆代工厂领域,台积电的3D封装技术一马当先,早在2008年底台积电就成立导线与封装技术整合部门,正式进军封装领域。据悉,台积电的3D封装工艺主要分为前端芯片堆叠SoIC技术和后端先进封装CoWoS和InFO技术。

2018年4月台积电首度对外界公布创新的SoIC技术。作为一种多芯片堆栈技术,SoIC可分为CoW(Chip on Wafer)和WoW(Wafer on Wafer)两种键合方式。其中,WoW就是将两层Die以镜像方式垂直堆叠起来,上述苹果M1 Ultral芯片以及今年年初Graphcore推出的IPU都采用的这种封装技术。

在2021年Hot Chips上,台积电公布了其SoIC研发进度,在CoW方面正在开发N7-on-N7和N5-on-N5等;WoW方面,则在开发Logic-on-DTC,预计2022年CoW和WoW将会实现基于N5工艺。

图片来源:台积电

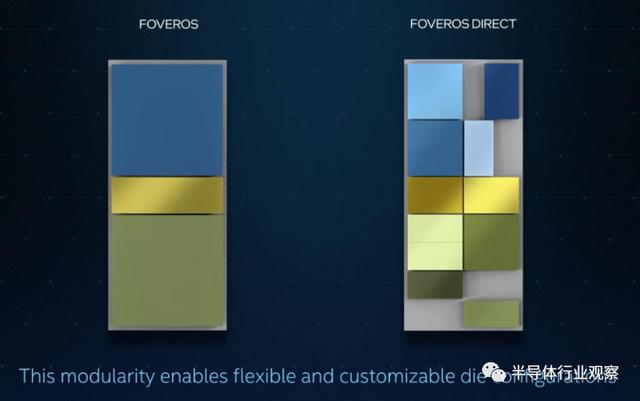

英特尔则是在2018年推出了3D堆叠封装技术“Foveros”,第一代 Foveros于2019年在Lakefield芯片中推出。英特尔方面预计在2023 年消费级处理器 Meteor Lake上使用其第二代 Foveros 技术,实现 36 微米的凸点间距,与第一代相比,连接密度有效地增加了一倍。除了第二代Foveros 技术外,英特尔预测第三代Foveros Omni以及第四代Foveros Direc都将在2023年量产。

图片来源:英特尔

三星在2020年8月公布了自家的3D封装技术“X-Cube”。据了解,X-Cube是一种利用垂直电气连接而不是电线的封装解决方案,三星在 7nm制程的测试过程中,成功利用 TSV 技术将SRAM 堆叠在逻辑芯片顶部,从而释放了空间以将更多的内存封装到更小的占位空间中。三星表示,这项技术将用于 5G、AI、AR、HPC(高性能计算)、移动和 VR 等领域。

中国大陆封测厂在3D封装技术领域也是频频发力。比如长电科技在五年7月推出了面向3D封装的XDFOI全系列极高密度扇出型封装解决方案,该技术所运用的极窄节距凸块互联技术能够实现44mm×44mm的封装尺寸,预计于2022年下半年完成产品验证并实现量产。而通富微电南通通富工厂则是在去年8月搬入2.5D/3D生产线首台设备——化学机械抛光设备(CMP),标志着该生产线全面进入设备安装调试和工程验证阶段。

此外,华为最近也有一项芯片堆叠封装专利曝光,在日前的分析师大会上,华为常务董事、ICT基础设施业务管理委员会主任汪涛指出,华为正尝试用堆叠芯片的相关技术,用不那么先进的芯片工艺也可以让华为的产品更有竞争力。

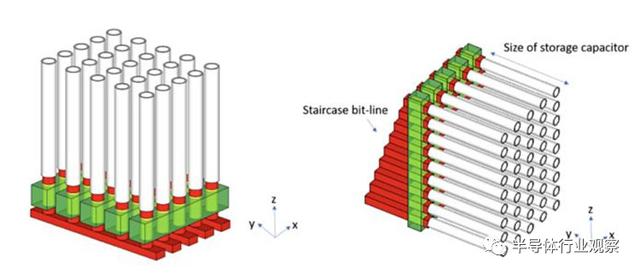

指日可待的3D DRAM

虽然与3D NAND同属于存储领域,但DRAM更多得是比拼工艺节点,制造工艺从 1x nm 缓慢推进到 1y、1z、1-alpha 和 1-beta,为此像三星、SK海力士和美光这三大DRAM厂商都已经拥抱了EUV技术,相比之下,3D进程就慢了很多,至今未有产品面市。

目前DRAM制造商仍在通过降低技术生产标准来提高存储单元的密度,并且通过向 EUV 扫描仪的过渡可以继续维持一段时间的平面技术,但这种资源也将很快耗尽,而对内存的需求却仍在攀升。由此来看,单元垂直排列,增加DRAM 体积才是未来趋势。

左边是传统的平面DRAM阵列,右边是垂直排列的单元(灰色长管是电容器)。

图片来源:Monolithic3D

瑞银投资银行全球研究部也指出,对于DRAM,使用EUV只能应对部分挑战,无法解决所有难题。采用3D DRAM是更有希望的解决方案,能缩小DRAM存储元件尺寸,从而提高密度。为此,瑞银投资银行全球研究部预计 3D DRAM最早可能于2027年开始初期生产到2028到29年开始实质性量产。

目前,几家存储大厂也开始逐渐向3D DRAM迈进。今年年初,BusinessKorea 报道称,三星电子正在加速 3D DRAM 的研发,已经开始加强招聘人员等相关团队建设。

此外,美光科技和 SK 海力士也在考虑开发3D DRAM。美光提交了与三星电子不同的 3D DRAM 专利申请,希望能在不放置单元的情况下改变晶体管和电容器的形状。也有日本媒体报道称,华为将在6月份举行的 VLSI Symposium 2022上发表其与中科院微电子研究所合作开发的 3D DRAM 技术。Applied Materials和Lam Research等全球半导体设备制造商也在开发与3D DRAM相关的解决方案。

不过,由于开发新材料的困难和物理限制,3D DRAM 的商业化还需要一些时间,业内人士预测,3D DRAM 将在 2025 年左右开始问世,虽然与瑞银投资银行全球研究部预计的时间有所出入,但不难看出,未来DRAM或许也将迎来3D DRAM的天下。

写在最后

每个时代有每个时代发展的瓶颈,但同时也有他们的破解之道。在芯片3D化过程中出现了很多新技术,这些新技术在打破平面技术发展极限的同时,也创造出新的难题、新的挑战,未来芯片竞争只会越来越激烈。

但“芯片有梦,技无止境”。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3056内容,欢迎关注。

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装