翻阅了一些关于数电教材,说实话,对一个有着十几年研发经验的老工程师我来讲,最大的感觉是 - 看着晕、吃力,虽然每本书都试图讲清楚每一个知识点的作用和前、后文的关联,但作为一个被各种新概念和逻辑公式绕晕的读者,确实已经无法get到这些点,进而理清楚由这些点构成的知识图谱。

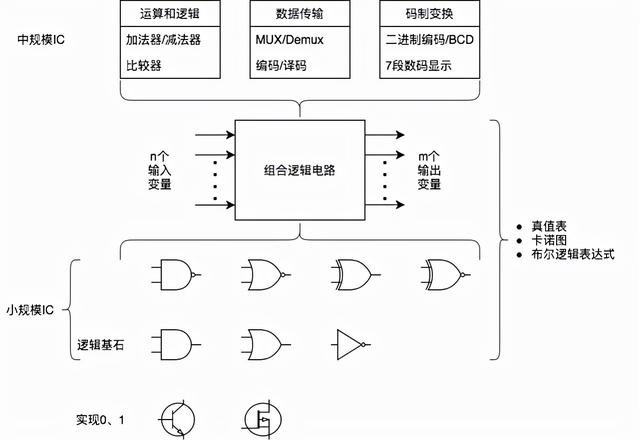

好在我从最初的二进制、各种门、布尔逻辑、卡诺图到编码/译码,已经学习完组合逻辑部分的内容,静下心来理出了些许的头绪,作为总结把这些点点滴滴的知识梳理一下,尝试着用下面的这幅图表达表达:

暂不管后面的时序逻辑,在这张图里,组合逻辑位于顶层,各种教材里基本上都作为重点讲述的一些逻辑功能 - 加法器、译码器等其实都是组合逻辑的一些典型案例而已,因为它们在某个年代因为是比较常用的数字功能块,被做成了专用的中等规模(被称之为MSI)的集成电路产品,比如74系列、CD4000系列中都有,做成专用的集成电路从实现的角度可以保证更高的可靠性、最佳的性能。

产业的发展,这些独立的功能模块IC已经很少被使用,当今一颗最小规模的FPGA就可以胜过几十个各种MSI模块的组合,而且更灵活、性价比高。它们当前存在的主要使命是用在教材里,用在有些实验室的实验平台里。

我们要加强的,就是要理解这些被重点强调的功能模块的实际应用场景,以及它们代表的一类产品的结构特点。

按照组合逻辑的定义,当前的2个或多个逻辑输入通过某种逻辑功能得到需要的逻辑输出,而这个输出只依赖于当前的输入。逻辑门是构成组合逻辑的基础,组合逻辑包括了以下3个部分:

- 输入变量,二进制,要么是0,要么是1,比如说有n个输入变量;

- 多个逻辑门构成的布尔逻辑;

- 输出变量,可以是多个,比如m个

在所有的教材里,讲述完“门”,紧接着就是一系列比数学公式还要抽象的布尔逻辑公式以及像极了数独游戏的卡诺图。多数的作业题都是给你一个用各种门构成的电路,让你进行“逻辑化简”;或者给你一个真值表,让你做”逻辑分析”,即便化简完、分析完,你面对的还是一个由多个门组成的电路图,其实还是不知道它们是用来做什么的。

到这里我基本上弄明白我为啥会“晕”的原因,因为我不知道自己所学的东西、所做的东西到底都是做什么用的?我在生活中如何会用到这些知识来解决问题?

这些教材试图让我提升的能力:根据一系列抽象的公式和工具,对一系列抽象的图做抽象的“简化”和“分析”。

这些,在今天这个时代实际上已经严重不合适,因为这方面的能力对于大多数人几乎无用武之地 - 我们要分析的对象已经被海量门阵列的FPGA代替,我们做的事情,EDA工具转瞬就帮我们实现,永远不再需要我们插手。

对于90%以上的同学,我们真正需要的能力其实是逻辑“表达”的能力,也就是对生活中、研发中遇到的任何一件事情,都能够把这件事情用数字逻辑的方式表达清楚,比如将要处理的事情分解成:

- 哪几个输入变量 - 有哪几种因素起作用?

- 哪几个输出变量 - 会得到哪几种结果?

- 输入变量和输出变量之间千丝万缕的关系是什么?

正确地分解成这三个部分,你完全可以借助EDA工具,无论是Verilog、VHDL甚至更高级的语言,都可以帮你完成您需要的逻辑。

即便从学习的角度,需要你去做底层的逻辑设计(IC设计)、需要你做逻辑化简和逻辑分析,正确的逻辑表达也是第一位的,因为它是解决一切应用的起点。

而这点,恰恰是我们众多的教材中欠缺的。

所以“组合逻辑”设计的逻辑应该是这么一个流程:

- 确定输入变量和输出变量的个数

- 将输入和输出变量都用字母表示

- 将输入和输出变量的关系描述出来

- 构建能够表达上述输入输出关系的真值表

- 获取针对每一个输出变量与输入变量之间关系的布尔表达式

- 简化针对不同输出变量的布尔表达式

- 基于简化的波尔表达式构建逻辑框图

可以采用多种不同的简化技巧以最小化布尔表达式,目的是减少门数,进而降低成本。这些技巧包括布尔算数理论、卡诺图化简,从硬件实现的角度,实现如下的目标:

- 尽可能少的门数,最少数量的输入

- 门和门之间的连接要尽可能少,传输时间尽可能短

如果基于以上的流程来理解教程中的知识点,就可以自上而下地理顺了它们之间的定位和关联,整个知识体系也就顺理成章了。

后面几节的内容,我们就来看看几种典型功能模块案例的实现方式,从原理图到用FPGA来验证。

,