可编程逻辑器件PLD(ProgRAMmable Logic Device),是在专用集成电路的基础上发展起来的一种新型逻辑器件,其主要特点就是完全由用户通过软件进行配置和编程,从而完成特定的功能,并且该器件可以反复擦写进行修改。

PROM——可编程只读存储器,Programmable Read Only Memory

PLA——可编程逻辑阵列,Programmable Logic Arrays

PAL——可编程阵列逻辑,Programmable Array Logic

GAL——通用阵列逻辑,Generic Array Logic

CPLD——复杂的可编程逻辑器件,Complex Programmable Logic Device

FPGA——现场可编程门阵列,Field-Programmable Gate Arrays

1、第一阶段——存储器

所谓存储器,就是一种用于长期存储大量数据、资料及运算程序等二进制信息的器件。存储器从存、取功能上可以分为只读存储器(ROM,Read Only Memory)和随机存储器(RAM,Random Access Memory)两大类。

1)只读存储器ROM

ROM,是一种存放固定信息的半导体,ROM中存储的信息是制造时由生产厂家一次写入的。这种器件在正常工作时只能读出信息,而不能写入信息,即使切断电源,器件中的信息也不会丢失。

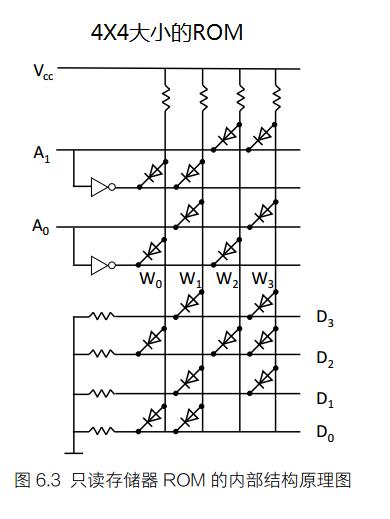

ROM是由地址译码器、存储矩阵、输出缓存器三个部分组成。

存储矩阵是由许多存储单元排列而成,存储单元是用二极管构成,也可以利用双极型三极管或MOS管构成,每个单元能存放1位二进制代码,每一个存储单元有一个对应的地址输入码。

地址译码器的作用是将输入的地址输入码译成相应的控制信号,利用这个控制信号从存储矩阵中将指定的存储单元选出,并把其中的数据送到输出缓冲器。

输出缓冲器的作用有两个,一是能提高存储器的带负载能力,二是实现对输出状态的三态控制,以便与系统的总线连接。

从ROM的结构框图中我们还可以看出,它有n位地址输入线,对应图上的A0~A(n-1),n位地址线经过地址译码器,可以译出2^n条译码输出线,对应图上的W0~W(2^n-1)。当给定一个地址输入码时,译码器只有一个输出被选中,这个被选中的线可以在存储阵列中取得m位的二进制信息,使其呈现在数据输出线F0~F(m-1)上,这m位的二进制信息称为一个字,因而W0~W(2^n-1)称为字线,F0~F(m-1)称为位线,字的位数又称为字长。

对于有n条地址输入线,m条位线的ROM,能存储2^n个字的信息,每个字有m位,每位可以存储一个0或一个1的信息,整个存储阵列的存储容量用字数乘位数来表示。因此我们可以称该ROM的存储容量为2^n X m。

从该电路内部原理图可以看出,该ROM具有2位地址输入码和4位数据输出。2位地址输入码A0和A1,能给出4个不同的地址,地址译码器将这4个地址代码分别译成W0、W1、W2、W3。它的地址译码器由8个二极管组成,其中每两个二极管就能构成一个与门,因此我们也可以将地址译码器称为与门阵列,只有当位线上的两个二极管同时截止的时候,位线才能选通,存储矩阵实际上是由4个二极管或门组成的编码器,当W0~W3每根线上给出高电平信号时,都会在D3~D0四根线上输出一个4位二值代码。

A0和A1就是地址线,W0~W3就是字线,D3~D0就是位线,字线和位线的每个交叉点都是一个存储单元。交点处接有二极管时相当于存1,没有接二极管时相当于存0。交叉点的数码也就是存储单元数,在读取数据时,只要输入指定的地址码,则指定地址内各存储单元所存的数据便会出现在输出数据线上。例如,当A1A0=10时,W2=1,而其他字线均为低电平。由于只有D2一根线与W2间接有二极管,所以这个二极管导通后使得D2为高电平,而D0、D1、D3为低电平,于是在输出端得到D3D2D1D0=0100。

2)可编程只读存储器PROM

ROM中固定信息是制造时存入的,产品出厂后用户无法改动,然而用户经常希望根据自己的需要来确定ROM的存储内容,为了满足这种要求,人们在ROM的基础上进行了修改,设计出了PROM(可编程只读存储器,Programmable Read Only Memory)。

PROM的总体结构和ROM一样,同样是由地址译码器、存储矩阵和输出电路组成,唯一不同的是PROM在ROM的原有二极管的基础上串了一个可熔断熔丝。因此PROM在出厂时将存储矩阵的所有交叉点全部制作了存储元件,相当于在所有存储单元中都存入了1,熔丝用很细的低熔点合金丝或多晶硅导线制成,在写入数据时只要设法将需要存入0的那些存储单元上的熔丝烧断就行了。因此,PROM的与门阵列是固定的,而或门阵列是可编程的,PROM的内容一经写入以后,就不能修改,所以他只能写入一次,我们也称PROM为一次可编程存储器。

PROM,虽然实现了可编程只读存储器,但是它只允许编程一次,这仍然不能达到人们的需要,因此又设计出了EPROM(Erasable Programmable Read Only Memory)可擦除、可重新编程的只读存储器。对已写入信息的EPROM,如果想改写,可用专用的紫外线灯照射芯片上的受光窗口,经过10~20分钟的时间,就能将芯片中的原有信息擦除掉,又可以写入需要的信息。

由于EPROM擦除操作需要紫外线或X射线,擦除时间也较长,而且只能整体擦除,不能单独擦除某一存储单元的内容,所以又设计出了EEPROM(Electrically Erasable Programmable Read Only Memory)电可擦除、可编程只读存储器,也称为E2PROM。E2PEOM擦除和编程都可用电完成,可整片擦除,也可使某数存储单元独立擦除,擦除时间可在10ms以内,而且它的重复编程次数大大高于EPROM。

3)随机存储器RAM

RAM,主要用来存放程序及程序执行过程中产生的中间数据、运算结果等。RAM可以按照需要随意地读写其内部存储单元的内容,且读写的速度与存储单元在存储芯片中的位置无关,它与ROM最大的区别就是:RAM在断电时将会丢失其存储内容,而ROM不会,所以RAM主要用来存储短时间使用的程序。

随机存储器RAM可以分为SRAM(Staic RAM)静态随机存储器和DRAM(Dynamic RAM)静态随机存储器。SRAM和DRAM的最大区别就是:DRAM是用电容有无电荷来表示信息0和1,所以为了防止电容漏电而导致读取信息出错,需要周期性的给电容充电,即刷新;而SRAM是利用触发器的两个稳态来表示信息0和1,所以不需要刷新。另外,SRAM的存取速度比DRAM快,价格比DRAM高,所以SRAM容量一般都比较小,常用作高速缓冲存储器Cache。DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM相比SRAM要便宜很多,计算机内存就是DRAM的。

2、第二阶段——可编程逻辑阵列PLA和可编程阵列逻辑PAL

一个2输入的ROM,需要4个与门;一个10输入的PROM,则要2^10个与门。在这种固定的与门阵列和可编程的或门阵列组合而成的结构中,随着输入端口的数量增加,我们可以发现与阵列的规模会急剧增加,器件的工作速度也会变慢。为了克服这种问题,人们便在PROM的机构基础上进行设计修改,设计出了PLA(Programmable Logic Arrays)可编程逻辑阵列和PAL(Programmable Array Logic)可编程阵列逻辑。

PLA不仅或门矩阵可以编程,与门阵列也是可以编程的,因此PLA的利用率较高,又由于PLA与阵列不采用全译码方式,所以在PLA中能够很好的解决随着输入变量的增加规模迅速增加的问题。但是,正因为PLA的与阵列、或阵列都是可编程的,导致了软件算法过于复杂,编程难度和费用上都有所增加,不可避免地使编程后的运行速度下降,PLA的使用受到了限制。因此,人们又设计出了可编程阵列逻辑PAL。

PAL的简易框架图正好与PROM相反,这种结构的与阵列也不是全译码方式的,因而具有PLA型结构速度快的优点。同时,它只有一个与阵列是可编程的,因而它编程容易实现,费用也比较低。

人们在PAL的基础上进行了改进,设计出了通用阵列逻辑GAL。GAL和PAL都是由可编程的与阵列和固定的或阵列组成,其区别主要是输出结构不同。

3、第三阶段——CPLD和FPGA

所谓复杂的可编程逻辑器件CPLD(Complex Programmable Logic Device),就是用户根据各自需要而自行构造逻辑功能的数字集成电路,是从PAL和GAL发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

所谓现场可编程门阵列FPGA(Field-Programmable Gate Arrays),就是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点,是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

1)复杂的可编程逻辑器件CPLD——以MAX3000A为例

从图中可以看出,它主要由逻辑阵列块(LAB,Logic Array Block)、宏单元(Macrocells)、可编程连线(PIA,Programmable Interface Array)和I/O控制块等四部分组成。宏单元是CPLD的基本结构,由它来实现基本的逻辑功能;可编程连线PIA负责信号传递,连接所有的宏单元;I/O控制块负责I/O电气特性控制;INPUT/GCLK1、INPUT/OE1、INPUT/OE2/GCLK2是全局时钟,清零和输出使能信号,这几个信号有专用连线与CPLD中每个宏单元相连,信号到每个宏单元的延时相同并且延时最短。

一个LAB,是由1~16个宏单元组成的。那么宏单元又是什么呢,上面就是宏单元的内部电路结构图。它的左边架构就是与门阵列和或门阵列,右边架构就是输出结构。

2)现场可编程门阵列FPGA

FPGA是大规模可编程逻辑器件除CPLD外的另一类器件。CPLD,是基于乘积项的可编程结构,也就是说,可编程的与门阵列和固定的或门阵列组成。而FPGA,则不同于CPLD的乘积项结构,它采用了一个全新的构架。

左边是传统的CPLD构架,由逻辑阵列LAB和可编程连线PIA组成,利用PIA将LAB互相连接起来,CPLD相对于老的PLD器件最大的进步主要是在于它能够在单个器件中容纳大量的逻辑。理论上,可以不断在CPLD中加入LAB,继续增加逻辑数量。但实际上,随着LAB的增加,可编程连线PIA则成指数型增加,布线资源占据了大量面积,直到芯片的连线数量超过了逻辑数量。因此,大容量的CPLD成本会非常高。如果我们能够省去全局布线资源,把LAB更加高密度的排列在器件内,而不是围绕在布线互连周围,情况会怎么样呢?

现场可编程门阵列FPGA便是如此,它没有采用中心全局器件互连,它将LAB排列在阵列中,布线放置在LAB之间的空格上,就像大城市的街道,这种布线被排列成行列互连的形式,它可以跨过器件的整个长度和宽度,或者器件的一小部分,只覆盖行列中的几个LAB。随着LAB的增加,它的布线资源是线性增加的,所以,这种结构可以实现大容量、低成本的逻辑器件。FPGA的LAB和CPLD的LAB设计也是不同的,CPLD的LAB是由宏单元构成,每个单元又是我们所熟悉的与门阵列和或门阵列结构;而FPGA的LAB从根本上抛弃了大量是由与门阵列和或门阵列的思路,它是由大量的逻辑单元LE构成,LE是基于查找表结构的。目前FPGA中多使用4输入的LUT,所以每个LUT又可以看成一个4位地址线的16X1的RAM。当用户通过原理图或者HDL语言描述一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果实现写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

从图中可以看出,它是一个4输入与门,所以只有4个输入都为1时,输出才会为1,其他情况就为0。我们用LUT实现的结果也是一样的,我们把输入当成地址,把RAM中存储的内容作为输出,我们只要将地址0000—1110内容全写0,只有1111内容写1,因此这两个电路完全等同。

4、FPGA的内部结构——以Cyclone IV为例

Cyclone IV器件主要是由逻辑阵列块(LAB,Logic Array Block)、嵌入式存储器块、嵌入式硬件乘法器、I/O单元和PLL等模块构成,在各个模块之间存在着丰富的互连线和时钟网络。随着FPGA的不断发展,FPGA芯片的内部结构也越来越复杂,并且包含的资源种类也越来越多。但是,FPGA最基本的架构还是由LAB、I/O单元和灵活多变的连线资源三个部分组成。

1)逻辑阵列块LAB

Cyclone IV器件的可编程资源主要来自逻辑阵列块LAB,每个LAB都是由多个逻辑宏单元LE(Logic Element)构成,LE在FPGA器件内部,用于完成用户逻辑的最小单元。

一个逻辑单元LE,主要是由一个4输入的查找表LUT(LookUp Table)、可编程的寄存器、进位链和寄存器链这四个部分组成。4输入的LUT可以完成所有的4输入1输出的组合逻辑功能。每一个LE的输出都可以连接到行、列、直连通路、进位链、寄存器链等布线资源。每个LE中的可编程寄存器都可以配置成D触发器、T触发器、JK触发器、RS触发器。每个可编程寄存器都具有数据、时钟、时钟使能、清零输入信号。LE有3个输出,一个驱动本地互连,另两个驱动行或列的互连资源。LUT和寄存器的输出可以单独控制,进而实现了在一个LE中,LUT驱动一个输出,而寄存器驱动另一个输出(这种计数称为寄存器打包)。因而在一个LE中的寄存器和LUT能够用来完成不相关的功能,能够提高LE的资源利用率。在一个逻辑阵列块中的LE还可以通过寄存器链进行级联。在同一个LAB中的LE的寄存器可以通过寄存器链级联在一起,构成一个移位寄存器,那些LE中的LUT资源可以单独实现组合逻辑功能,两者互不相关。Cyclone IV的LE可以工作在两种操作模式下,即普通模式和算术模式。普通模式下的LE适合通用逻辑应用和组合逻辑应用的实现;算术模式下的LE可以更好的实现加法器、计数器、累加器和比较器。

2)I/O单元

I/O单元是可编程输入/输出单元(IOB)的简称,它是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求,比如从基本的LVTTL/LVCOMS接口到PCI/LVDS/RSDS甚至各种各样的差分接口,从5V兼容到3.3V/2.5V/1.8V/1.5V的电平接口。为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每组能够独立地支持不同的I/O标准,通过软件的灵活配置,可匹配不同的电器标准与IO物理特性,而且可以调整驱动电流的大小,可以改变上下拉电阻。Cyclone IV设备有8个IO bank(组)。

3)灵活多变的连线资源

FPGA中的布局布线资源主要包括三部分:连线盒CB(Connection box)、开关盒SB(Switch box)和行列连线。布线资源是为了能够让位于不同位置的逻辑资源块、时钟处理单元、BLOCK、RAM、DSP和接口模块等资源能够相互通信,从而协调合作,完成所需功能。

FPGA中的布线资源,就好比绘制PCB板时的连线资源一样,虽然器件A和器件B的位置和连接关系没有任何改变,但很可能因为周边电路的布局、布线的一些变化,使得前后两次A、B之间的连线形态发生很大的变化。因此,与采用固定长度的金属线将所有宏单元连接在一起的CPLD不同,FPGA中任意两点之间的线延迟是无法预测的,必须等到布局、布线完成之后才能确定。这也是为什么在FPGA开发中,时序约束和时序分析这两样工作是必不可少的。

,