有些人对高速信号都是很难理解,为什么信号要绕一下?象蛇一样扭来扭去。有些基础的人就知道这是为了一组线能等长。那为什么要等长?等长误差又是怎么算的?这些就不是很清楚了。一般是SI工程师告诉他要怎么布等长。

今天卧龙庄主就给大家讲讲这个为什么要等长,等长误差怎么计算的问题?

高速信号比如DDR信号,是并行传输的。数据线一组,地址线一组。数据在从电路板的一端经过PCB导线传到另一端,是有延时的。虽然只有几ns,基至几十ps,但对高速信号来说,这点时间偏差就会致命。

欢迎在加入电子技术交流圈,积级分享知识,大家一起共享知识!

DDR在数据传输时,是通过时钟采样的。当一组信号从一端传到另一端时,时钟会进行采样,然后实现读,写过程。如果这组信号线不是同时传过来的,到达时间不一样,时钟就采样不到整个数据了。或者这组信号是同时传过来的,但时钟与这组信号有些延时,那就会在采样时,采样不到正确的数据。

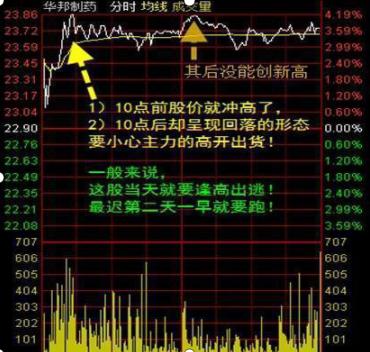

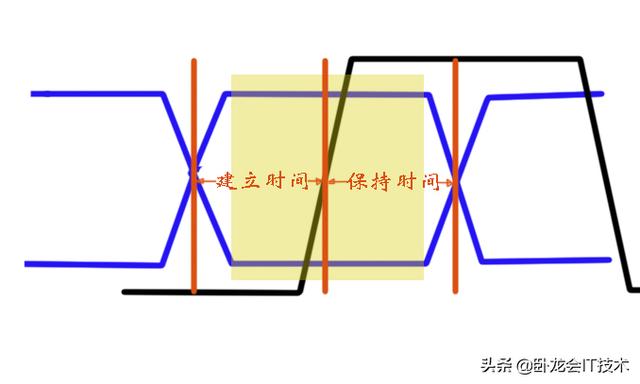

说说地址线与时钟这间的关系吧。它们之间的正常的话,关系如下图所示

图1

蓝色为地址信号,黑色为时钟信号。正常的话,时钟信号上升沿一般在地址信号的中间,这时采样到的数据是最准确的。如果在两端,因信号处在上升,下降沿,此时电平并不是很准确。图中黄色透明的区域是能准确采样到数据的范围。

这里红色标出了建立时间,保持时间。 一般芯片DATASHEET中都有这个建立时间,保持时间。时钟与地址线必须符合这个建立,保持时间,系统才能正常运行。

上面是正常的情况,地址线与时钟线完全等长的情况。那如果不等长会怎么样呢?我们再来看看下面的图

图2

蓝色地址线比时钟线延时了一段时间。时钟上升沿向后移了,结果超出了这个黄色透明区域。这个时候时钟采样的数据就不对了,系统肯定死掉了。这就是为什么要等长的原因。

二,等长误差计算那这个等长要控制在多少呢。其实就是时钟上升沿不能移出这个黄色透时区域就可以。计算方法就是先查芯片上的建立时间(Tsetup),保持时间(Thold)。原创今日头条:卧龙会IT技术。

仿真出来后,上图红色字体所示的建立时间及保持时间是不是满足芯片手栅上的Tsetup,Tholed。时钟与地址线的这个等长误差裕量就是在黄色透明区域。不过,还需要考虑时钟抖动,数据抖动等等,这个裕量还需要于减小一点。这些参数都要在芯片手册上去找出来。然后仿真计算出来。

今天就分享到这!

想知道更多电子技术。

请关注本头条号@卧龙会IT技术,感谢支持!

原创:卧龙庄庄主

卧龙会,卧虎藏龙,电子行业高手汇聚!

,