我们经常听到新闻里报道尖端芯片制程时,常常提到几纳米几纳米制程,比如台积电最牛逼,3纳米已经开始试产,并已经开始2纳米制程的开发。欧盟也在最近公布的芯片法案内抱怨欧洲即使研究成果领先世界,但是实际生产都集中在22纳米大小的车载芯片领域,7纳米5纳米的芯片都做不了,更不用说3纳米甚至2纳米了。

芯片尺寸越来越小意味着功耗越来越小

可见纳米制程是衡量一个企业,甚至一个国家芯片制造水平的重要标志。那这到底代表什么哪一段的长度?为什么这么难达到?

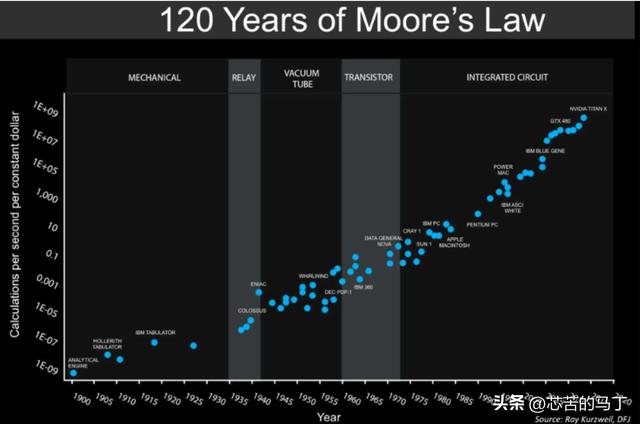

要搞清楚纳米制程是什么,我们先了解下芯片制造领域一个著名的定律-摩尔定律。

英特尔前任总裁Gordon Moore在1965年4月19日的《电子学》(Electronics)技术期刊上发表了摩尔定律,当时还是仙童公司电子工程师的摩尔在《电子学》杂志上发表文章预言,半导体芯片上集成的晶体管和电阻数量将每年翻一番。1975年他又提出修正说,芯片上集成的晶体管数量将每两年翻一番。目前修订的说法是每18个月翻一番。

当时,集成电路问世才6年。摩尔的实验室也只能将50只晶体管和电阻集成在一个芯片上。摩尔当时的预测听起来好像是科幻小说;此后也不断有技术专家认为芯片集成的速度“已经到顶”。但事实证明,摩尔的预言是准确的。尽管这一技术进步的周期已经从最初预测的12个月延长到如今的近18个月,但“摩尔定律”依然有效。目前最先进的集成电路已含有17亿个晶体管。

摩尔定律

这就意味着指数级增长的晶体管排列在一定区域的芯片上,甚至芯片也在变得越来越小。这就意味着晶体管之间的排列更紧密,晶体管也越来越小。经常提到的2纳米或者7纳米,指的是单个晶体管栅极的长度,当晶体管工作时,电流要从漏极流向源极,此时要通过栅极,这个栅极就好比电门,宽度就是所谓得2纳米或者7纳米制程了。纳米作为单位长度,很多人没有概念。1毫米等于1000微米,1微米等于1000纳米,大家可以想象下精密程度。

但在把芯片越做越小后,晶体管两级之间会产生漏电现象,所以如何控制电子的有效流动,如何在更小的芯片上摆放更多的晶体管,就是考验芯片设计和制程能力的挑战。谁掌握这个技术,在芯片制造领域就有绝对话语权,因为更小的制程意味着更小的芯片,同时意味着更少的能耗,更大的空间留给了其他设备,也让智能穿戴设备的发展成为可能。

虽然现在晶体管结构已经从MOSFET平面结构发展为立体的鳍式场效应晶体管结构,或是全环绕栅极晶体管结构,纳米制程已经不像以前那样有参考意义,但依旧被用来衡量芯片制造技术的一个重要指标。

FinFet和GAA工艺

,