将半导体和无源器件等多个不同器件集成进单个封装,或微型化的模块,就叫系统级封装(SiP)。这样做可以实现特别快速和低成本的开发周期。本文将重点介绍专门针对射频应用开发SiP实现的关键优势,以及像Insight SiP这样的公司是如何通过交钥匙统包(Full-Turnkey)设计服务,以及如何运用自己先进的封装设计方法帮助客户取得成功的。

射频系统集成采用SiP方法已经成为微型化路线中的关键。尽管在单个裸片中集成越来越多的功能(系统级芯片概念)是一种长期趋势,但小型个人设备复杂性永无止境的增长在不断推进人们使用SiP实现完整的系统。射频SiP可以使用多种技术实现,每个制造供货商都有自己特殊的方面;因此SiP实现需要根据不同的材料、物理沉积方法和属性进行裁剪,以适应特定的设计规则。

不管采用哪种封装/组装技术,比如有机基板(BT、FR4……)、多层陶瓷基板(LTCC、HTCC、厚膜……)、线绑定、倒装芯片,还是硅或玻璃上的薄膜集成无源器件(IPD)等等,设计公司合作伙伴能够在封装内将其射频专业知识与独特的功能嵌入能力结合起来很重要。

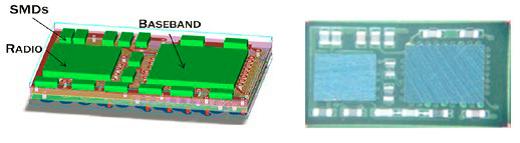

图1显示了Insight SiP公司开发的两款SiP产品例子。

图1:射频SiP例子和物联网可穿戴SiP封装。

射频SiP上增加超小型天线从而形成所谓的“内置天线封装”产品(AiP)一直是ATD(先进技术开发)的一个基础部分。这种技术已经在低功耗蓝牙(BLE)和超宽带(UWB)应用的无线产品中得到成功实现。

为什么SiP方法可以满足今天的挑战

随着嵌入越来越复杂功能的消费电子产品的大规模普及,新设备满足低功耗、更小长宽比要求,同时保持很强的价格竞争力非常重要。因此,工程师和产品开发团队面临着多方面的挑战,包括缩小节点不再必然降低每个晶体管成本(从65nm以后)的事实、SoC开发时间、非重复性工程成本(NRE)和故障风险随着每代节点的发展不断攀升以及高增长市场(物联网、汽车……)要求在小空间内高成本效益地集成不同功能(内存、MCU、GPU、模拟器件、射频器件、MEMS、CIS……)。

更低功耗已经替代更快速度成为最重要的IC要求,而且器件需要通过现有的射频协议(比如蜂窝),或新兴的网络(比如像LoRa、SigFox、LTE-M、NB-IoT等LPWAN)实现无线连接。只有SiP方法能够帮助满足这些典型要求,因为这种系统划分可以提供超越摩尔定律的能力,SiP的模块化可以简化将不同功能增加到数字SoC中的实现。与将多个独立封装的裸片安装到印刷电路板上相比,在一个IC封装中封装多个裸片可以使功耗降低3到10倍。

多裸片IC设计和制造流程正在不断成熟,它们可以降低 NRE并缩短开发时间,从而使得SiP对中小批量来说也有不错的经济性。那些已经发布许多基于中介层的IC产品的IDM和无工厂IC供应商现在正在抓紧生产中,并且在开发更多这样的2.5D-IC设计。诸如台积电(TSMC)等大的开放型代工厂也在自己的多裸片封装线上投入了巨资,而大多数大的OSAT公司已经开发并提供WLP解决方案。此外,多家EDA供应商提供用户友好的建模与设计工具,这些工具不仅可以用来最大限度地缩短开发时间和降低风险,还能降低多裸片IC的单价。

根据TechSearch International作出的统计,2015年交付的SiP产品达133亿个,其中几乎70%是射频和连接模块,见图2。

图2:根据器件类型划分的2015年SiP市场。(来源:Techsearch International)。RF Modules: RF模块

今天的高性能半导体应用主要受带宽和功耗的限制。三星、IBM、Intel、HiSilicon、英伟达等公司已经展示了在中介层上以堆叠或并排方式整合多个裸片的优势。与在PCB上安装单独的IC相比,非常短的裸片到裸片连接以及非常宽的总线可以显著提高性能,同时降低功耗。今天增长最快的半导体机会(移动设备、汽车和物联网节点)需要众多不同的功能与周边环境发生交互。在单个SiP中整合多个不同的裸片和传感器可以满足它们对空间、功耗和成本的约束要求。

可用于无缝集成的先进设计方法

为了满足射频和消费类SiP产品的快速增长要求,Insight SiP公司开发出了一种私有的先进设计方法,这种方法将电磁仿真(3D EM)与电路级仿真和优化结合在一起。作为一个整体策略,在建立第一个原型之前执行详尽的前端电磁仿真可以减少工程样品反复的次数;进而帮助最终用户节省成本,缩短产品的上市时间。

图3总结了这种先进的设计流程。这种方法组合使用电路和电磁仿真工具创建设计,从基本的原理图描述逐步过渡到完整的3D版图电磁描述。制造只在完整版图得到完全仿真后才开始进行;2.5D或3D电磁仿真用于无源器件集成(层压、LTCC、IPD),谐波平衡或Spice建模用于有源电路。

图3:Insight SiP公司独特的设计方法。

图4显示了完整的设计流程,从基于初始原理图的电路仿真一直到经过完全仿真和测试的版图。

图4:一直到经过测试的版图的Insight SiP公司设计流程。

S parameters: S参数,

Active circuits: 有源电路;

parametrical/mechanical: 参数的/机械的

objects: 对象

S parameters: S参数

for each object: 对每个对象

circuit simulation: 电路模拟

EM/Circuit simulation: EM/电路模拟

Layout/EM: 布局/EM

Circuit design: 电路设计

buried function design: 埋入功能设计

Layout design: 版图设计

substrate manufacturing: 基板制造

multi-layers/thin film: 多层/薄膜

test of buried functions: 埋入功能测试

SiP final test: SiP最终测试

图5给出了一个使用这种专门方法的射频SiP例子。这是为智能手机应用开发的产品,历时6个月(从设计到功能样机)。其中包含一个GPS收发器芯片、一个数字基带芯片和一些无源器件(6×4mm, VFPGA封装)。

图5:GPS SiP例子。

对于内置天线封装(AiP)设计来说,这种基于扩展3D电磁仿真的设计流程可以帮助设计师评估在辐射、增益、效率和覆盖范围等方面最佳的天线性能。这是射频调谐第一批工程样品期间优化工作的关键。下面给出了典型的仿真输出结果。

本文描述的所有SiP或MCM优势都是与安装在PCB上的单裸片SoC比较的结果,后者是使用最为广泛的制造工艺。除了最近晶圆和面板级工艺的成本下降工作在继续外,多裸片IC的设计和制造生态系统的快速成熟也催生了高价值的解决方案。

在对合适的SiP设计公司合作伙伴作出判断时,工业化和生产支持是关键因素。像Insight SiP等公司可以访问世界领先公司对每种SiP制造技术与封装作出的设计规则,因此允许为每个定制项目选择最高效的工艺与生产组合。

与不同的OSAT制造合作伙伴保持紧密的关系非常重要,特别是对复杂的射频系统来说,而Insight SiP公司已经与诸如Amkor、AT&S、Tong-Hsing、Kyocera、 SPIL……等主要供应商建立了强大的合作关系。这是在工业化过程中保证产品供货安全和良率改进的关键优势(例如在扩大生产过程中的射频/天线调谐)。

图6:仿真得到的天线性能。

本文来自《电子工程专辑》2017年4月刊,版权所有,谢绝转载

,