当我们谈论MOSFET的寄生电容时,我们在谈论什么?

EE工程师都会面临MOSFET的选型问题,无论是功率级别应用的Power MOS还是信号级别的Signal MOSFET,他们的Datasheet中,一定会给出MOSFET的三个结电容随Vds电压变化的曲线。之所以需要关心这些电容,是因为电容容值从某些层面反映了器件的开关特性,影响了包括开关速度、效率、振荡以及EMI在内的各种系统特性。

相信很多EE第一次面对这些寄生电容时,都会觉得玄乎其玄。为什么电容不再是固定的容值,而非要随着DS的电压急剧变化?现实世界往往是非线性和复杂的,今天本着格物致知的精神,我们先从功率MOSFET器件的结构出发,让大家明白MOS里面的这些寄生电容到底是什么,以及怎样对应到实际的电路应用中来,帮助大家形成一些知识上的闭环。

1.横向沟道与垂直沟道

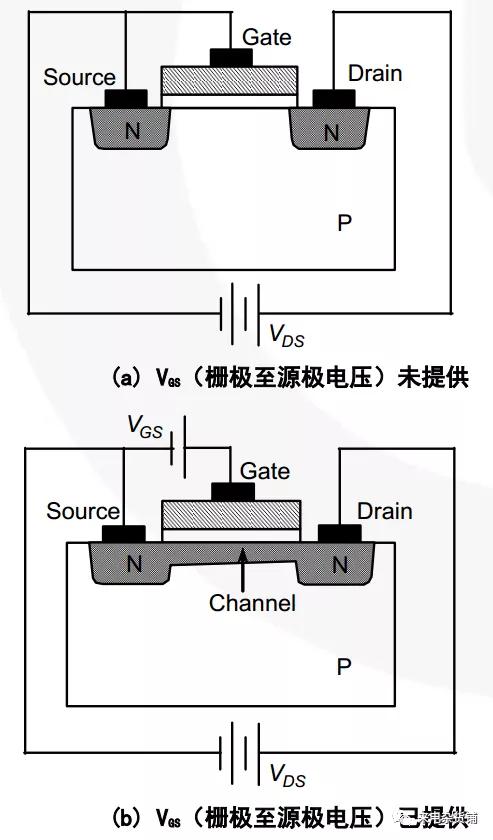

所谓沟道Channel,本质上就是电流在MOS本体中的流通路径。可以看到,沟道的开通与否是由栅极Gate与源极Souce之间的Vgs电压决定,因此MOSFET被认为是电压控制型器件。

如下这张示意图是横向沟道设计,漏源极之间距离小且都置于硅晶圆表面,这样的结构适合集成,多用于信号级的MOS。

功率MOS一般采用的垂直沟道设计,源极和漏极置于晶圆的相反两端。以常见封装TO-220为例,芯片置于框架上,通常将靠近塑封料的一面称为正面,正面主要分布源极和门极,靠近铜框架的一面称为背面,背面主要分布漏极。这样从漏极连到源极的沟道的方向就是“垂直的”。

2.垂直沟道MOS的半导体结构

衬底substrate、外延层epitaxial layer和本体P- Body,和高掺杂N 区构成了垂直沟道MOSFET的半导体结构。

如下a)图,是最早期投入商业应用的VMOS设计,但由于制造的稳定性问题和V形槽尖端的高电场, VMOSFET被取代。

如下b)图,为DMOSFET设计(Fairchild的叫法),可以看到其栅极Gate与表面平行,又称平面型MOS,这是商业上最成功的设计,由于工艺简单,至今还有非常大的年出货量。

当然,当前主流的功率MOS的门极结构如下c)图,使用U型槽设计,称为UMOSFET,或直接称为沟槽型MOS。

可以看到无论哪种结构,MOS的Gate都会与N 区,P- Body区,以及外延层形成一对多的局面,这也是MOS的门极相关电容的主要来源。

3.电容在哪儿?

当我们从应用层考虑寄生电容对电路性能影响时,对于MOS管及其结电容一般采用如下的方式进行建模。

同时,厂家也会在Datasheet中给出Ciss,Coss和Crss的典型值和曲线。如果只是停留在主功率电路的设计层面,工程师只需要知道这些电容的大致范围即可。但在调试过程中,往往需要关注到更细节的瞬态波形,对电容特性的理解就显得至关重要了。

上图为一个MOSFET元胞的纵向截面,只展示左边这一半,右边的一半可以轴对称看过去。一个MOSFET产品往往由成千上万个这样的元胞横向重复并联组成,因此需要有单位面积电容的概念。

Cgs,是栅极对源极的电容。在芯片尺度,这个电容由三部分组成:栅极对源极金属的电容Co,栅极对N 区的电容CN ,栅极对P- Body的电容Cp。在芯片表面,源极金属,N 区和P- Body,都是等电位的。因此栅极对源极的电容容值是以上三个电容容值之和。

其一,栅极对源极金属的电容Co可以表示成:

公式中的物理量意义解释如下

当器件栅极结构确定时,Ao 和to都是确定的值,Co可以认为是固定值。

其二,栅极对N 的电容CN 可以表示为:

公式中的物理量意义解释如下

一些专用仿真软件,对MOS进行物理层面的建模时,Cox是非常典型的一个参数,它反映了栅极氧化物的电容性质。可以认为,Cox也是固定的结构参数,CN 不随Vds电压变化。

其三,唯一随电压变化的就是栅极对P- Body的电容 Cp了。在Vds的低压段,当VDS增大时,耗尽区会扩大至p型体,耗尽区的厚度决定了电容CP的极间距,容值随之减小。但到一定程度后耗尽区的厚度不再增大,不会超过P- Body的10%,最终表现为Cp在高压段随Vds电压变化极小。

Cgd,是栅极对漏极的电容,又称米勒电容。其中,平面型MOS的单位面积的米勒电容可以由以下公式计算如下:

其中,Wd为外延层中耗尽区的宽度。X为表面外延层的横向长度。当DS电压越高时,耗尽区的宽度越大(根据PN结理论,表面外延层中耗尽区的宽度Wd和Vds电压的平方根成正比),有效的米勒电容的极板面积减小,米勒电容容值减小。

Cds,漏源极电容。这个电容的容值大小与P-Body和外延层的接触结构强相关(上图是非常理想的平面型接触,是为了方便大家有一个定性的理解。实际上商用MOSFET的接触结构更多的是三维的,将空间充分利用起来,例如如SuperJuction MOSFET)。这样的结构可以按如下PN结的结电容公式计算:

可以看到,漏源电容也随着Vds的增加而减小,和Vds的平方根成反比,这也是大多数电力电子教科书中近似量化Vds电容非线性的一种方法。

经过以上的介绍,相信大家都对MOS的结电容有了初步的认识吧。这里我们提出两个问题,留给读者自己查询资料,下期也会给出答案。

- 我们知道,半导体性质随温度的变化非常明显,那么MOS的结电容和温度的相关性大吗?

- 怎样去测量各个电压下这三个寄生电容的容值呢?

回答了“为什么”和“是什么”的问题,下一期,我们通过具体实例给出寄生电容在电路系统中的应用表现,回答“怎么办”的问题。

该内容是小编转载自来电杂货铺,仅供学习交流使用,如有侵权,请联系删除。如果你还想了解更多关于电子元器件的相关知识及电子元器件行业实时市场信息,敬请关注微信公众号 【上海衡丽贸易有限公司】

,