FinFET

单晶硅具有准金属的物理性质,有较弱的导电性,其电导率随温度的升高而增加,有显著的半导电性。超纯的单晶硅是本征半导体, 基本上不导电。

本征半导体(intrinsic semiconductor)是指完全不含杂质且无晶格缺陷的纯净半导体,一般是指其导电能力主要由材料的本征激发决定的纯净半导体。 典型的本征半导体有硅(Si)、锗(Ge)及砷化镓(GaAs)等。 本征半导体是指化学成分纯净的半导体,它在物理结构上有多晶体和单晶体两种形态,制造半导体器件必须使用单晶体。 制造半导体器件的半导体材料的纯度要达到99.9999999%,常称为“9个9”。 在制造半导体器件的过程中会进一步提高材料的纯度,单晶体不但纯度高,在晶格结构上也是没有缺陷的, 用这样的单晶体制造的器件才能保证质量。

在硅晶体中掺入微量的A族杂质原子(如磷、砷、锑等),可形成N型半导体,电子(带负电)是其导电的主要载流子。这是因为这些杂质原子和硅原子形成共价键结构时,其外围五个电子中的四个会留下一个电子不受共价键束缚而成为自由电子,于是N型半导体就成为了含电子浓度较高的半导体,其导电性主要是因为自由电子导电

如图1.1所示

在硅晶体中掺入微量的ⅢA族杂质原子(如硼、铟等),将形成P型半导体,空穴(带正电)是其导电的主要载流子。这些杂质原子和硅原子形成共价键结构时,其外围只有三个电子,比硅原子少了一个电子而留下了一个空缺,即空穴。当空穴被其他邻近的电子补上时, 那补位的电子原先的位置便又留下了一个新的空穴,这个空穴的转移 可视为正电荷的运动,成为能够导电的载流子(见图1.2)。

N型半导体和P型半导体是所有半导体器件的基础。掺杂的杂质浓度越高,半导体导电性越好,电阻率越低。

1.2 PN结二极管在一块完整的硅片上,用不同的掺杂工艺使其一边形成N型半导体,另一边形成P型半导体,两种半导体的交界面附近的区域称为PN结。

在P型半导体和N型半导体结合后,由于N区内自由电子为多数载流子(多子),空穴几乎为零,称之为少数载流子(少子),而P区内空穴为多子,自由电子为少子,在它们的交界处就出现了电子和空穴的浓度梯度。由于存在自由电子和空穴浓度梯度的原因,有一些电子从N区向P区扩散,也有一些空穴从P区向N区扩散。它们扩散的结 果就使P区一边失去空穴,留下了带负电的杂质离子,N区一边失去电子,留下了带正电的杂质离子。开路中半导体中的离子不能任意移动,因此不参与导电。这些不能移动的带电离子在P区和N区交界面附近,形成了一个空间电荷区,见图1.3。空间电荷区的薄厚与掺杂浓度有关。

在空间电荷区形成后,由于正负电荷之间的相互作用,在空间电荷区形成了内建电场,其方向是从带正电的N区指向带负电的P区。显然,这个电场的方向与载流子扩散运动的方向相反,将阻止载流子的进一步扩散。

另一方面,这个电场将使N区的少数载流子空穴向P区漂移,使P区的少数载流子电子向N区漂移,漂移运动的方向正好与扩散运动的方向相反。从N区漂移到P区的空穴补充了原来交界面上P区所失去的空穴,从P区漂移到N区的电子补充了原来交界面上N区所失去的电子,这就使空间电荷减少,内建电场减弱。

因此,漂移运动的结果是使空间电荷区变窄,扩散运动加强。最后,多子的扩散和少子的漂移达到动态平衡。在P型半导体和N型半导体的结合面两侧,留下离子薄层,这个离子薄层形成的空间电荷区称为PN结。PN结的内建电场方向由N区指向P区。在空间电荷区,由于缺少可移动载流子,所以也称之为耗尽区。

1.3 双极型晶体管双极型晶体管由两个PN结构成,其中一个PN结称为发射结,另一个称为集电结。两个结之间的一薄层半导体材料称为基区。接在发射结一端和集电结一端的两个电极分别称为发射极和集电极,接在基区上的电极称为基极见图1.5。

在应用时,发射结处于正向偏置,集电极处于反向偏置。通过发射结的电流使大量的少数载流子注入到基 区,这些少数载流子靠扩散迁移到集电结而形成集电极电流,只有极少量的少数载流子在基区内复合而形成基极电流。集电极电流与基极电流之比称为共发射极电流放大系数。在共发射极电路中,微小的基极电流变化可以控制很大的集电极电流变化,这就是双极型晶体管的电流放大效应。双极型晶体管可分为NPN型和PNP型两类。这种晶体管的工作,同时涉及电子和空穴两种载流子的流动,因此它被称为双极性的,所以也称双极性载流子晶体管。因为其需要较大的面积和能耗,制造和设计的成本较高,其重要性已远不如MOSFET,目前主要用在模拟电路中。

图1.5 双极结型晶体管剖面结构示意图

1.4 金属-氧化物-半导体场效应晶体管

MOSFET

一块薄层半导体受横向电场影响而改变其电阻的现象称为场效应。利用场效应,使自身具有放大信号功能的器件称为场效应器件。在这种器件薄层半导体的两端接两个电极称为源和漏。控制横向电场的电极称为栅。根据器件栅、源漏以及沟道结构的不同,场效应晶体管可以分为以下几种:

①采用金属-绝缘体-半导体的系统构成的金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor ,MOSFET) ;

②采用PN结构成栅极的结型场效应管 (Junction Field-Effect Transistor,JFET);

③采用金属与半导体接触肖特基势垒结构成栅极的MESFET场效应晶体管;

④高电子迁移率晶体管(HEMT),这种器件在结构上与MESFET类似,但是在工作机理上却更接近于MOSFET。

⑤无结金属-氧化物-半导体场效应晶体管 (Junctionless Field-Effect Transistor,JLFET);

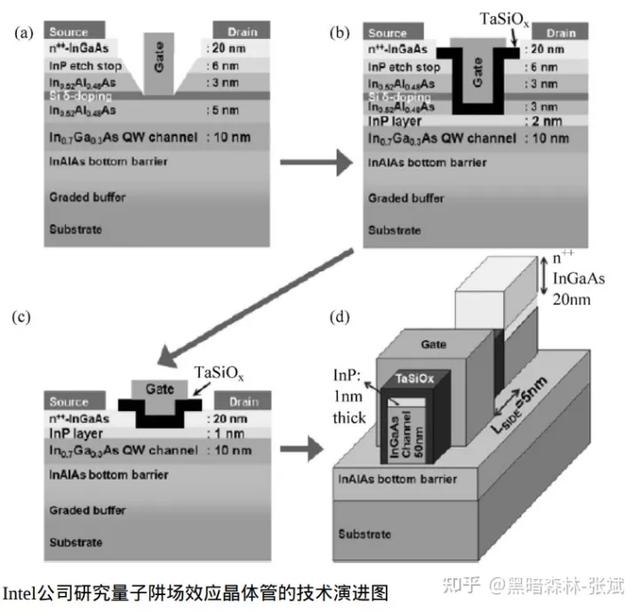

⑥量子阱场效应晶体管。

一对N沟道和P沟道MOS管以推挽形式(推挽方式可完全独立产生高低电平,推挽方式为低阻,这样,才能保证口线上不分走电压或分走极小的电压(可忽略),保证输出与电源相同的高电平,推挽适用于输出而不适用于输入,因为若对推挽(低阻)加高电平后,I=U/R,I会很大,将造成口的烧毁。适用于大功率输出)工作,构成互补的金属氧化物半导体器件 ( Complementary Metal-Oxide-Semiconductor,CMOS)。其组成的反相器基本电路单元所实现一定逻辑功能的集成电路称为CMOS电路。其特点是:

①静态功耗低,每门功耗为纳瓦级;

②逻辑摆幅大,近似等于电源电压;

③抗干扰能力强,直流噪声容限达逻辑摆幅的35%左右;

④可在较广泛的电源电压范围内工作,便于与其他电路接口;

⑤速度快,门延迟时间达纳秒级;

⑥在模拟电路中应用,其性能比NMOS电路好;

⑦与NMOS电路相比,集成度稍低;

⑧有“自锁效应”,影响电路正常工作。

图1.8为当代先进CMOS器件结构示意图

结型场效应晶体管(Junction Field-Effect Transistor,JFET)是在同一块N型半导体上制作两个高掺杂的P区,并将它们连接在一起,所引出的电极称为栅极(G),N型半导体两端分别引出两个电极,分别称为漏极(D)和源极(S),如图1.11所示。结型场效应晶体管通过栅极电压改变两个反偏PN结势垒的宽度,并因此改变沟道的长度和厚度(栅极电压使沟道厚度均匀变化,源漏电压使沟道厚度不均匀变化),进而调节沟道的导电性来实现对输出电流的控制,是具有放大功能的三端有源器件,也是单极场效应管中最简单的一种,它可以分N沟道或者P沟道两种。

1966年,一种金属-半导体场效应管(Metal-Semiconductor FET, MESFET)被提出并在一年后实现,它在结构上与结型场效应管 (JFET)类似,不过它与后者的区别是这种场效应管并没有使用PN结作为其栅极,而是采用金属-半导体接触所构成的肖特基势垒结的方式形成栅极,如图1.12所示,其沟道通常由化合物半导体构成,它的速度比由硅制造的结型场效应管JFET或MOSFET快很多,但是制造成本相对更高。但是金属-半导体接触可以在较低温度下形成,可以采用GaAs衬底材料制造出性能优良的晶体管。

MESFET热稳定性较差、漏电流较大、逻辑摆幅较小、抗噪声能力较弱。随着频率、功率容限以及低噪声容限需求的增加,砷化镓MESFET已经达到了其设计上的极限,因为满足这些需求需要更大的饱和电流和更大跨导的短沟道场效应器件。一般可以通过增加沟道掺杂浓度来实现。由于沟道区是对体半导体材料的掺杂而形成的,多数载流子与电离的杂质共同存在。多数载流子受电离杂质散射,从而使载流子迁移率减小,器件性能降低。