在中大功率电源中,现在市面上最流行的拓扑结构可谓是移相全桥和LLC了,工程师们也最喜欢将这它们放在一块作比较,这是由于它们的原边MOS管都可以实现ZVS,从而降低损耗,提高了功率密度。但它们也各有不同的优缺点,这里我们来分析一下移相全桥的工作特点,而LLC在前段时间发的《频率是怎样影响LLC增益的》中已分析过,这里就不再详细描述。

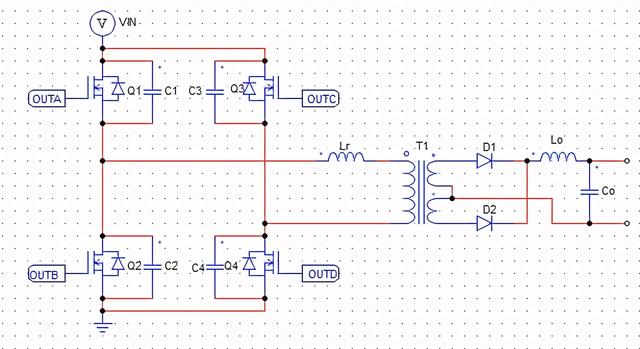

移相全桥,顾名思义,首先它的硬件拓扑是一个全桥结构,而“移相”的意思是控制方式采用移相方式。我们知道PWM和PFM的控制原理,那么“移相”控制的控制原理是什么呢?接下来,我们就此说道说道。

UCC2895是经典的移相全桥控制芯片,图1是它datasheet中的时序图。CLOCK是芯片的时钟,决定了芯片工作频率;RAMP与环路输出的COMP信号做比较,决定移相角度大小PWM SIGNGAL,PWM SIGNAL占空比为0时,移相角度为180°,占空比为100%时,移相角度为0。

图1

图2是驱动的信号的接对应MOS管的驱动方法。在PWM驱动方式控制中,一般是直接控制对管的Q1/Q4、Q2/Q3的驱动信号占空比大小。而在移相方式中,不直接改变单个开关管的驱动占空比,而是保持每个开关管驱动占空比为50%,通过改变驱动信号相位的方式来改变对管同时导通时间,从而调节输出。所以实际上“移相”也是一种特殊PWM控制方式。

图1中,OUTPUTA/OUTPUTB相位超前于OUTPUTC/OUTPUTD,所以我们称图2中的Q1和Q2为超前桥臂,Q3和Q4为滞后桥臂。超前桥臂比滞后桥臂更容易实现ZVS,这是为什么呢,后面将会作出解释。

图2

图3

图3展示了移相全桥工作的实现波形图,其中Ip为谐振腔的电流,Vrect为变压器副边电压,其值等于VIN/N,N为变压器匝比。Vrect波形的阴影部分是丢失的波形,即在实际中这部分时间没有能量传递到输出,相当于这部分MOS管的占空比被间接丢失了,导致有效占空比变小,这在设计时应该考虑补偿占空比。

为什么会出现这种现象呢?这是因为这个时间段的原边电流较小,不足于提供输出电流,而副边电感维持输出电流使得D1、D2均导通,相当于副边绕组短路。随着下一组对管的同时导通,电流迅速增大到一定值才能将能能量传递到输出。而此时原边电流增大的速率与谐振电感Lr大小有关,Lr越大,电流增大的速率越小,使得丢失的占空比越大,所以Lr越小越好?讨论这个问题时,我们会涉及到前文提到的“超前桥臂比滞后桥臂更容易实现ZVS”的问题。

首先我们要知道原边MOS管是如何实现ZVS的,它是通过电感电流不能断续的特性来抽取MOS管寄生电容Cds的电能,以此使得在MOS管开通前Vds降为0。例如,图2中,Q1关断后,Lr电流继续流向变压器,在Q2开通前,其电流回路只能通过C1和C2,此时,C1是充电,C2是放电。其实这个时候,不仅是Lr参与抽取电流,输出电感Lo通过变压器映射到原边也参与抽取电流,但对于Q3、Q4的关断时刻,由于丢失占空比,副边绕组相当于短路Lo不能映射到原边,不参与抽取电流,所以Q3、Q4相比于Q1、Q2更难实现ZVS。

综上,谐振电感Lr太大会导致丢失占空比严重,不利于调节控制;Lr太小不利于实现原边MOS管的ZVS,所以在设计时需要综合考量,选择适合Lr。一般可以通过以下两个方程选择Lr的的大小。

其中,Dloss为丢失占空比,fsw为开关频率,Io为输出电流。

最后我们对比一下LLC和移相全桥的异同。

|

序号 |

对比项 |

LLC |

移相全桥 |

|

1 |

控制方式 |

PFM |

移相 |

|

2 |

原边MOS管ZVS的实现 |

在全电压、全负载范围内均可实现 |

超前桥臂比滞后桥臂容易实现,重载比轻载容易实现。 |

|

3 |

副边整流管ZCS的实现 |

开关频率小于等于谐振频率时可实现 |

不能实现 |

|

4 |

EMI问题 |

较轻 |

较严重 |

|

5 |

输入(或输出)范围调节能力 |

较窄 |

宽 |

|

6 |

是否需要输出电感 |

否 |

是 |

|

7 |

同等条件下的效率 |

较高 |

较低 |

|

8 |

能否使用半桥拓扑 |

可以 |

可以,但需要三电平的半桥拓扑 |

移相全桥仿真波形

,