凡是挂在总线上的存储器芯片或外设,为了区分,必须由地址译码电路为每个存储芯片或外设提供一个与地址信息有关的片选信号。当CPU访问存储器或外设时,出现在AB总线上的地址信号可划分为两部分,直接与存储器或外设连接的地址线可称为片内地址线,其所用根数与存储器的容量有关,容量为2 n ;其中,n为片内地址线的根数;剩余的地址线称为片外地址线,可作为译码电路的片选地址线。如图4-6所示为常见译码分类方式。

图4-6 常见译码分类方式

常用的存储器地址空间分配方法有两种:线性选择法(简称线选法)和地址译码法(简称译码法),下面分别进行介绍。

1. 常规译码法

(1)线选法

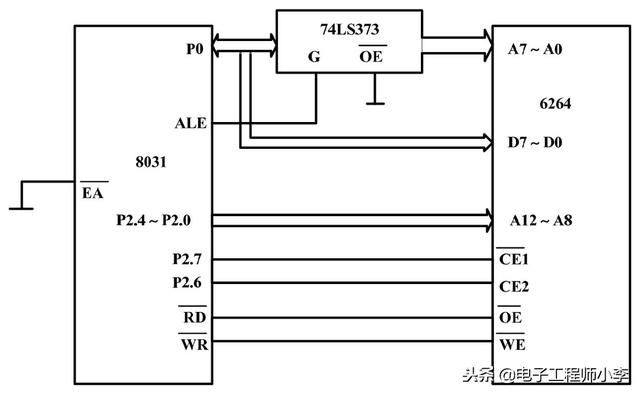

线选法就是直接利用单片机片外地址线或某端口的I/O线直接与存储器芯片或外设接口的片选引脚线连接。线选法的优点是电路简单,不需要另外增加地址译码器硬件电路,体积小,成本低。缺点是可寻址的芯片数目受到限制,适用于芯片较少而且片选线充足的系统。另外,地址空间不连续,每个存储单元的地址不唯一,这会给程序设计带来不便,只适用于外扩芯片数目不多的单片机系统的存储器扩展。如图4-10所示为单片机线选法。

图4-10 单片机线选法

注意: 若有多条片选线时,在CPU访问存储器期间只能有一根处于有效状态,不允许出现多条片选线同时有效的现象。

(2)译码法

所谓的译码法就是使用地址译码芯片对系统的片外地址进行译码,以其译码输出作为存储器芯片或外部设备的片选信号。这种方法能够有效地利用存储器空间,适用于多芯片的存储器扩展。译码法又分为完全译码和部分译码两种。常用的译码器芯片有74LS138(3线-8线译码器)、74LS139(双2线-4线译码器)和74LS154(4线-16线译码器)。

完全译码:地址译码器使用了全部地址线,其特点是地址与存储单元一一对应,即存储器的每一个存储单元只有唯一的一个地址与之对应,不存在地址重叠现象。

部分译码:地址译码器仅使用了部分地址线,地址与存储单元不是一一对应,而是一个存储单元占用了几个地址。使用1根地址线,一个单元占用2(2 1 )个地址;使用2根地址线,一个单元占用4(2 2 )个地址;使用3根地址线,则占用8(2 3 )个地址,依次类推。

思考: 要扩8片8KB的RAM 6264,如何通过74LS138把64KB空间分配给各个芯片?

由74LS138真值表可知,把G1接到 5V,

接地,P2.7、P2.6、P2.5(高3位地址线)分别接74LS138的C、B、A端,由于对高3位地址译码,这样译码器有8个输出Y0~Y7,分别接到8片6264的各片选端,实现8选1的片选。低13位地址(P2.4~P2.0,P0.7~P0.0)完成对选中的6264芯片中的各个存储单元的单元选择,这样就把64KB存储器空间分成8个8KB空间了。64KB地址空间分配如图4-11所示。

图4-11 64KB地址空间划分成8个8KB空间

这里采用全地址译码方式。因此,51单片机发出16位地址时,每次只能选中某一芯片及该芯片的一个存储单元。

思考: 如何用74LS138把64KB空间全部划分为4KB的块?

4KB空间需12条地址线,而译码器输入只有3条地址线(P2.6~P2.4),P2.7没有参加译码,P2.7发出的0或1决定选择64KB存储器空间的前32KB还是后32KB。由于P2.7没有参加译码,就不是全译码方式,前后两个32KB空间就重叠了。那么,这32KB空间利用74LS138译码器可划分为8个4KB空间。如果把P2.7通过一个非门与74LS138译码器G1端连接起来,如图4-12所示,就不会发生两个32KB空间重叠的问题。这时,选中的是64KB空间的前32KB空间,地址范围为0000H~7FFFH。如果去掉图4-12中的非门,地址范围为8000H~FFFFH。把译码器的输出连到各个4KB存储器的片选端,这样就把32KB空间划分为8个4KB空间。P2.3~P2.0,P0.7~P0.0实现单元选择,P2.6~P2.4通过74LS138译码实现对各存储器芯片的片选。采用译码器划分的地址空间块都是相等的,如果将地址空间块划分为不等的块,可采用可编程逻辑器件FPGA对其编程来代替译码器进行非线性译码。如图4-13所示为74LS138地址译码电路。

图4-12 存储空间被划分成每块4KB

图4-13 74LS138地址译码电路

地址分配:

CS_LED: 0x8000~0x8FFF; LED指示灯片选地址

CS_SHUMA: 0x9000~0x9FFF; 数码管片选地址

CS_A/D: 0xA000~0xAFFF; A/D转换器片选地址

CS_D/A: 0xB000~0xBFFF; D/A转换器片选地址

CS_LCD: 0xC000~0xCFFF; 液晶片选地址

CS_KEY_RD: 0xD000~0xDFFF; 读键盘片选地址

CS_KEY_WR: 0xE000~0xEFFF; 写键盘片选地址

首先看LED指示灯的地址控制端CS_LED为什么是0x8000~0x8FFF,74LS138首先要工作,必须将片选输入

端置为有效,根据硬件连接,

已经接地,这时只需要将E3置为高电平即可随时启动该74LS138芯片,又由于把单片机的最高位地址线A15接在了E3上,所以,所有外设的片选地址都必须让A15位置为高电平1,这样,74LS138片选输出就完全取决于C(A14)、B(A13)、A(A12)这3个控制端,显然要让LED指示灯的地址控制端CS_LED有效,也就是让74LS138的Y0输出端有效(为0),只需要C(A14)=0、B(A13)=0、A(A12)=0即可,也就是说只要让单片机地址总线的高4位为1000,而其他12根低地址线可以任意取0和1,所以到此便推算出了LED指示灯的片选地址是0x8000~0x8FFF。同理,数码管、A/D转换器、D/A转换器、液晶、键盘也是如此。但是在这里,有些读者不难发现一点,键盘的片选信号为什么有两个,一个“读键盘地址”,一个“写键盘地址”,关于这一点,本书会在键盘设计部分详细说明。 注意: 地址的分配是随具体硬件连接的不同而变化的。只要硬件连接固定了,外设地址也就固定了。

(3)地址译码关系图

在设计地址译码器电路时,如果采用地址译码关系图,将会带来很大的方便。如图4-14所示即为一地址译码关系图。

图4-14 地址译码关系图示例

从图4-14中可以看出以下几点:

① 属完全译码还是部分译码。

② 片内译码线和片外译码线各有多少根。

③ 所占用的全部地址范围为多少。

在上面的关系图中,有1个“·”(A15不接),表示为部分译码,每个单元占用两个地址。片内译码线有11根(A10~A0),片外译码线有4根。其所占用的地址范围如下:当A15为0时,所占用地址为0010000000000000~0010011111111111,即2000H~27FFH。当A15为1时,所占用地址为1010000000000000~1010011111111111,即A000H~A7FFH。共占用了两组地址,这两组地址在使用中同样有效。

2. 简化译码法

从上面设计的各个外部设备模块中不难发现,每一个模块的74LS374或者74LS574的CLK端都用到了一个或门或者或非门作为选通逻辑,这样,如果外部设备很多,势必要用很多类似的逻辑门电路,那么是否可以节省一下呢?大家仔细研究一下不难发现,每个逻辑都是放在74LS138地址译码的后面,不妨换个思维考虑,如果将一个合适的逻辑门放在74LS138前面,是否可以实现“总体逻辑”呢。如图4-15所示,74LS138的两个地电平控制端

直接接地,而其高电平控制端E3是由单片机的

、

两个信号“与非”后得到的,当单片机不读写任何外部设备时,两个信号均为高电平,与非门输出低电平,74LS138不工作,输出高阻,由于其外部加了上拉电阻,故7个外部设备片选信号均为高电平,程序一旦读写外部设备,两个信号其中必有一个要变为有效(即低电平),导致与非门输出高电平,74LS138开始工作,其输出也就是8个片选信号必有其一被选中(变为低电平),当两个信号变高的一瞬间(其实在一次读写过程中只有其一有效,所以这里只是针对其中一个而言),与非门输出又变为低,再次导致74LS138停止工作,输出高阻,而刚才的片选信号由于有外部上拉电路的作用,迅速从被选中状态(低电平)上跳到高电平,这样便完成了后续外部设备74LS374 CLK端所需要的上升沿信号,也就将数据输出到外部设备或者读入外部设备的数据。

图4-15 74LS138译码前加读写逻辑

3. 高级译码法

一般的单片机系统设计中,译码电路基本上都是采用类似74LS138的译码芯片,但是还有另一种功能非常强大的常用通用逻辑芯片,那就是可编程逻辑器件GAL。有经验的工程师可能都非常喜欢用这种芯片,如GAL16V8、GAL20V8这两种最常用的芯片,因为通过对这种器件编程,完全可以取代一般单片机设计中用到的所有译码逻辑芯片,编程方便,可以在不改变硬件连接的情况下对外围设备重新进行地址分配,大大节省了开发时间,同时也降低了电路板的占用面积,提高了系统的稳定性。但是另一方面,该芯片价格稍贵,大概8~10元/片,大大高于74LS138芯片,所以还是要在设计时权衡速度和成本,以做出最优化设计。如图4-16所示是利用GAL20V8B设计的译码电路。

图4-16 GAL20V8B实现小规模全功能译码

,