任务书如下:

实验报告如下:

一、社会调研与资料查阅

调研对象:锁具市场和各大小区的门禁系统。

工作过程与方法:经过在各种锁具市场的走访,发现国内大部分人使用的还是机械锁。而且,当下的假冒伪劣产品泛滥成灾,互开率非常高,互开率,是指各种锁具的一个技术质量标准,也就是一把钥匙能开几把锁的比率。

二、需求分析

1.系统功能目标

设计一个电子密码锁,实现设置修改密码和开锁的功能

(1)基本功能

① 可设置并保存四位密码数字,并在数码管中显示1111;

② 先按开锁键,之后开始输入密码,并显示;若三次输入错误,则锁定,需要按解锁键,并输入解锁密码(固定为0)后再次尝试;

③ 密码输入错误和密码输入正确均有相应的提醒信息(如LED亮或蜂鸣器发声等);

④ 可删除输入的数字,删除的是最后输入的数字。

(2)扩展功能

当前输入的数字在最右侧数码管显示,前面输入的数字自动左移一个数字位置。

2、输入输出方案

用预置的密码0007先开锁

设置新密码0076

关锁并验证新密码0076

输入三次错误的密码进入锁定状态

输入解锁密码接触锁定

三、系统设计方案

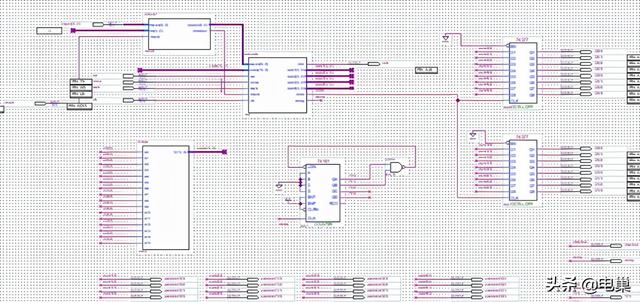

1.功能模块图

(1)密码输入控制模块

引脚:

inputs[9…0]:密码输入

en[3…0]:使能

check:开锁键

outputs[9.0]:密码输出结果

checkout:输出校验信号

上边为输入密码的控制模块,en为计数器的计数值,当en为0011即密码已经输入错误三次的时候,阻塞这个inputs和check信号。

(2)密码锁控制模块

各个信号说明

Clk—时钟信号

back–删除键,每按一次back,最后输入的数字将被删除,密码显示右移一位,最高位补0。

check–密码校验信号–锁关着时,输入密码按check,则比较看是否开锁

set–修改密码–锁打开时,输入密码按set则将密码送入锁存器所存,密码显示电路清零。

close–关锁信号–在锁开着时按下close,锁将被锁上.

store–存密码的信号

wrong–密码输入错误的信号,让外部计数器计数一次

code—寄存器中存储的密码

lock—锁是否打开的状态信号,1代表锁被打开,0代表锁关闭

num—输入的密码

(3)存储密码模块

用2个8位寄存器74377扩展为一个16位寄存器,用来存储密码(每四位二进制代表一位十进制密码)

(4)计数模块

此模块用来检验密码输入错误的次数,如果输错三次,会给密码输入控制模块一个激励信号,阻塞用户的输入,只有当输入解锁密码后才能再次输入。

(5)七段译码模块

用四个七段数码管7447来动态显示密码的输入。

2、技术方案论证

(1)技术可行性

EDA技术是随着集成电路和计算机技术的飞速发展而产生的一种高级、快速、有效的电子设计自动化工具。它是为解决自动控制系统设计而提出的,从70年代经历了计算机辅助设计(CAD),计算机辅助工程(CAE),电子系统设计自动化(ESDA)三个阶段。第三代EDA工具根据工程设计中的瓶颈和矛盾对设计数据库实现了统一管理,并提出了并行设计环境概念,提供了独立于工艺和厂家的系统级的设计工具。EDA关键技术之一就是采用硬件描述语言对硬件电路进行描述,且具有系统级仿真和综合能力。目前应用比较广泛的硬件描述语言就是Verilog HDL。

Verilog HDL和VHDL一样,是目前大规模集成电路中最具代表性、使用最广泛的硬件描述语言之一。Verilog HDL有如下优势:

1>能够在不同的抽象层次上,如系统级、行为级、RTL级、门级和开关级对设计系统进行精确而简练的描述。

2>能够在每个抽象层次上对设计进行仿真验证,及时发现可能存在的错误,缩短设计周期,并保存()整个设计过程的正确性。

3>语法类似于C语言,学习和掌握比较容易。

四、阶段进度计划与成本考虑

1、阶段进度计划:

2、方案成本调研

七段数码管:4个

按键与开关:

印刷电路板:

FPGA芯片:4位二进制同步加法计数器74161、七段数码管7447、8位寄存器74377

五、系统实现

1、功能块的实现

(1)设置密码

在锁打开的情况下,设置一个新密码0076,密码锁控制模块hui 输出一个store信号,该信号传到寄存器模块的时钟上升沿,存储密码。

(2)开锁

我们用新设置的密码,再次尝试开锁,当lock置1说明锁成功打开

(3)密码输入

用10位二进制数字开关代表十进制数字0-9,即最终用16位二进制来存储四位十进制密码,每次输入密码的过程都是输出据左移的过程。

(3)密码删除

删除密码的过程就是数据右移的过程。

(4)输入信号控制

计数器计数的值是密码输入错误的次数,一旦输错三次就会将输入信号阻塞,除非输入解锁密码0000000001,才会解除这种阻塞状态。

2、仿真分析

功能仿真(前仿真):

功能仿真是指在一个设计中, 在设计实现前对所创建的逻辑进行了验证其功能是否正确的过程。 布局布线以前的仿真都称作功能仿真, 它包括综合前仿真( Pre-Synthesis Simulation )和综合后仿真( Post-Synthesis

Simulation )。 综合前仿真主要针对基于原理框图的设计 ; 综合后仿真既适合原理图设计 , 也适合基于 HDL 语言的设计。

时序仿真(后仿真)

时序仿真使用布局布线后器件给出的模块和连线的延时信息, 在最坏的情况下对电路的行为作出实际地估价。 时序仿真使用的仿真器和功能仿真使用的仿真器是相同的, 所需的流程和激励也是相同的; 惟一的差别是为时序仿真加载到仿真器的设计包括基于实际布局布线设计的最坏情况的布局布线延时, 并且在仿真结果波形图中,时序仿真后的信号加载了时延, 而功能仿真没有

(1)开锁

先用预置的密码0007开锁,在输入的时候由于是用10位二进制代替十进制数据输入,所以依次输入000000001,0000000001,0000000001,0010000000,并在时钟上升沿给出check开锁信号,观察到下面lock信号由0->1,说明已经成功开锁。

(2)设置密码

在锁打开之后,我们再次输入一个6,即此时电路中的密码为0076,我们给出set信号,此时lockcode模块会将激励信号store传到寄存器的时钟端给出一个时钟上升沿来将密码锁存,存储成功后在七段数码管中显示1111(观察p3p2p1p0)。

我们现在尝试用新设置的密码再次开锁,先在时钟上升沿给一个close信号,让锁处于关闭状态,然后依次输入0076(就是刚设置的新密码),再次在时钟上升沿给出check信号验证密码,通过下面的仿真图观察到lock的状态由0变到1,说明锁再次被成功打开。

(3)删除当前输入的一位密码

给出删除信号back,我们观察密码的变化,由0076变为0007,说明成功将当前输入的密码删除。

(4)测试三次输入错误锁定状态。

我们首先输入close信号将锁关闭,然后输入一个错误的密码0006,并连续给出三次check信号,我们观察到计数器的值依次为0001、0010、0011,已经试过三次错误的密码,然后再输入密码5,此时电路中的密码为0065,再次给出check信号,观察到password的值仍旧为0006,说明此时已经成功的进入锁定状态,最后一次的输入并没有送到电路中去。

3、引脚分配表

六、展望

1.问题与解决

问题一:不知道怎么实现输入三次错误密码阻塞输入信号

解决:通过加一个输入信号的控制模块,通过判断计数器的值来决定是否将输入信号阻塞在控制模块。

问题二:模块集成的时候出现了问题

解决:通过小组开会讨论,及时仿真测试等手段排除了故障。

2、系统不足与扩展展望。

大多信号需要手动输入,离全自动化的实现还有一段距离。

『本文转载自网络,版权归原作者所有,如有侵权请联系删除』

,