信号的沿产生在当信号状态发生相应的改变时。逻辑结果的沿产生在当操作数的逻辑运算结果与之前的逻辑运算结果相比较发生了改变。 下表解释了两种沿检测的差异。

1、信号边沿检测

在功能块图 ( FBD ) 与梯形图 ( LAD ) 中边沿检测是通过功能 “ POS ” ( 上升沿 ) 与“NEG ” ( 下降沿 )实现的。 第一次操作数的状态( 例如, 输入位 I1.1 ) 与之前查询的信号状态进行比较 (例如,I1.1 )。如果实际信号状态=1, 查询之前的信号状态=0, 那么将认为产生一个上升沿并且功能“POS ” 的输出将被置为1。为了“POS ” 能够比较 I1.1 的实际信号状态与之前的状态,每一次查询的实际信号状态将缓存在标志位中以便用于下一次查询。

在功能块图中信号上升沿与下降沿检测的例子。

信号上升沿与下降沿检测的信号图的例子。信号“E1.2 " 为复位信号。

2、逻辑结果边沿检测

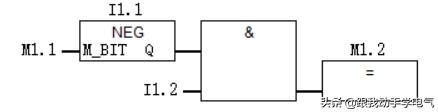

在 FBD 与 LAD 中实现逻辑结果边沿检测是通过“P ”(上升沿) 与 “ N ” (下降沿) 实现的。如果逻辑运算结果改变, 例如从0 到1,则该扫描周期中“P ” 输出的信号状态为“1 ”(见信号图)。为了使该功能能够识别出沿的变化, 该逻辑结果必须存储在沿的标志位中 (例如, M1.1 )。

在功能块图中逻辑结果的上升沿与下降沿检测的例子。

逻辑结果上升沿与下降沿检测的例子。